---

САНКТ-ПЕТЕРБУРГСКИЙ ПОЛИТЕХНИЧЕСКИЙ

УНИВЕРСИТЕТ ПЕТРА ВЕЛИКОГО

---

**С. А. МОЛОДЯКОВ**

**АРХИТЕКТУРА ЭВМ**

**Часть 1. Основы организации ЭВМ**

**Учебник**

Санкт-Петербург

Издательство Политехнического университета

2019

УДК 004.2: 004.35: 004.431.4

Молодяков С.А. Архитектура ЭВМ. Часть 1. Основы организации ЭВМ.

Учебник. СПб.: СПбПУ, 2019.- 330 с.

В учебнике представлен материал лекций, которые читаются по дисциплине «Архитектура ЭВМ» в высшей школе программной инженерии СПбПУ. В первой части «Основы организации ЭВМ» рассмотрены вопросы, связанные с кодированием данных, организацией процессоров, памяти и внешних устройств, а также рассмотрено программирование на языке Ассемблера.

Учебник предназначен для студентов, обучающихся по направлениям подготовки 09.03.04 «Программная инженерия» и 02.03.02 «Фундаментальная информатика и информационные технологии», изучающих дисциплины «Архитектура ЭВМ», «Программирование периферийных устройств» и др.

© Молодяков С. А. 2019

© Санкт-Петербургский политехнический

университет Петра Великого

# Оглавление

|                                                                                                    |     |

|----------------------------------------------------------------------------------------------------|-----|

| ГЛАВА 1. БАЗОВАЯ ОРГАНИЗАЦИЯ ЭВМ .....                                                             | 6   |

| 1.1. Многоуровневая организация и эволюция ЭВМ. ....                                               | 6   |

| 1.2. Архитектурные принципы Фон-Неймана .....                                                      | 11  |

| 1.3. Магистральная вычислительная структура.....                                                   | 15  |

| 1.4. Процессор. Основные компоненты и их назначение.....                                           | 18  |

| 1.5. Программная модель процессора Pentium. ....                                                   | 21  |

| 1.6. Оперативная память (общая характеристика).....                                                | 24  |

| 1.7. Типовая структура машинной команды в пространстве и во времени. Формат и конвейер команд..... | 27  |

| ГЛАВА 2. ВИДЫ ДАННЫХ, ИХ КОДИРОВАНИЕ, КОМАНДЫ.....                                                 | 36  |

| 2.1. Числа и системы счисления.....                                                                | 38  |

| 2.2. Представление и команды над целыми числами .....                                              | 40  |

| 2.3. Форматы чисел плавающей запятой, команды.....                                                 | 51  |

| 2.4. Кодирование символов .....                                                                    | 58  |

| 2.5. Графические данные, их представление и кодирование .....                                      | 66  |

| ГЛАВА 3. ПРОЦЕССОР .....                                                                           | 88  |

| 3.1. Процессор – аппаратный уровень. Операционные устройства .....                                 | 88  |

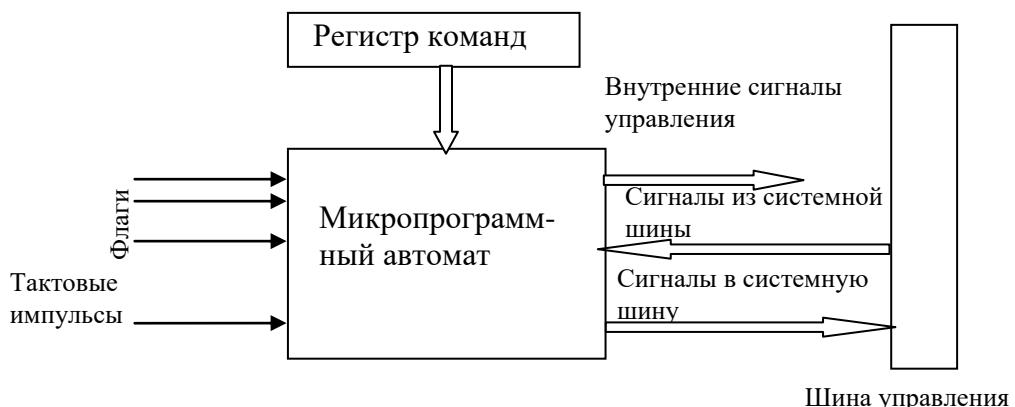

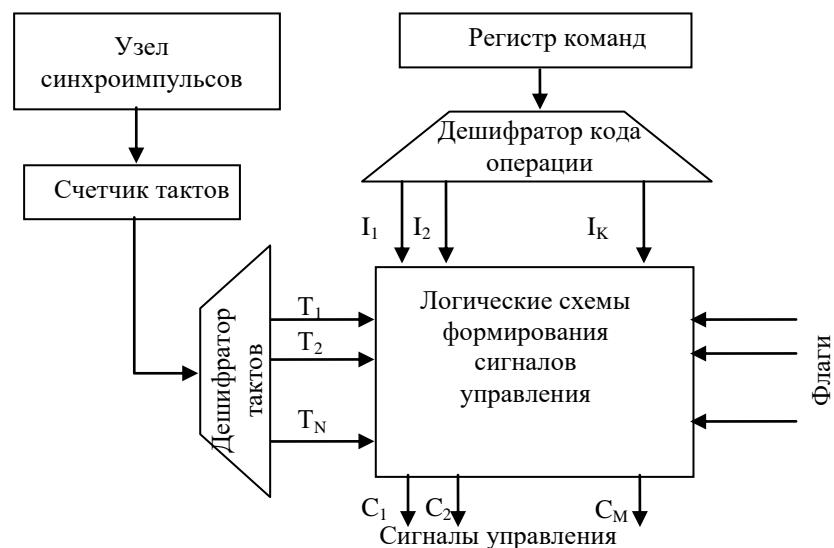

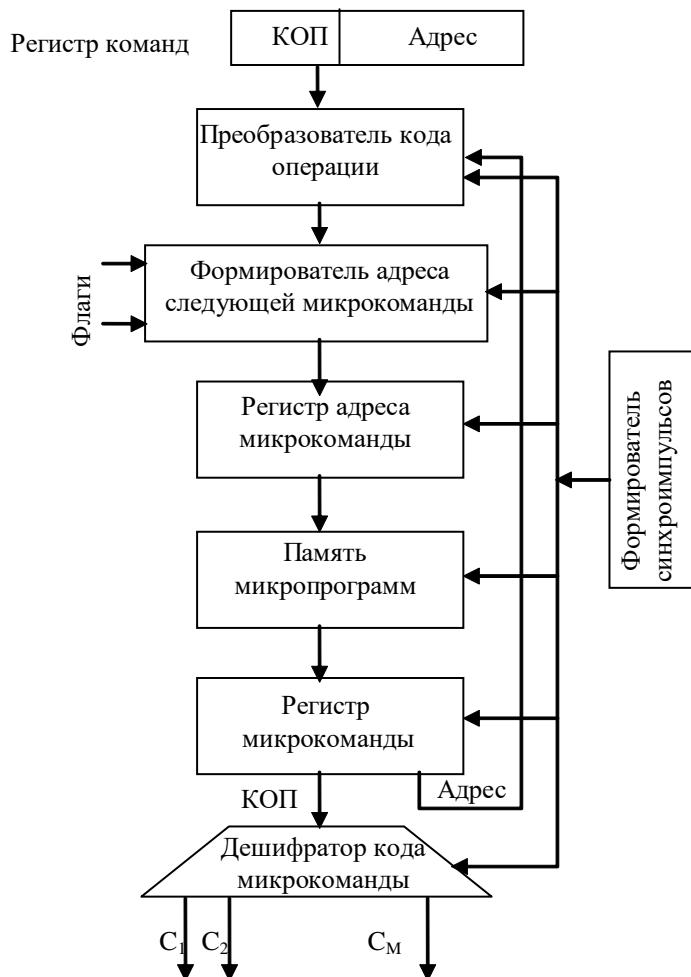

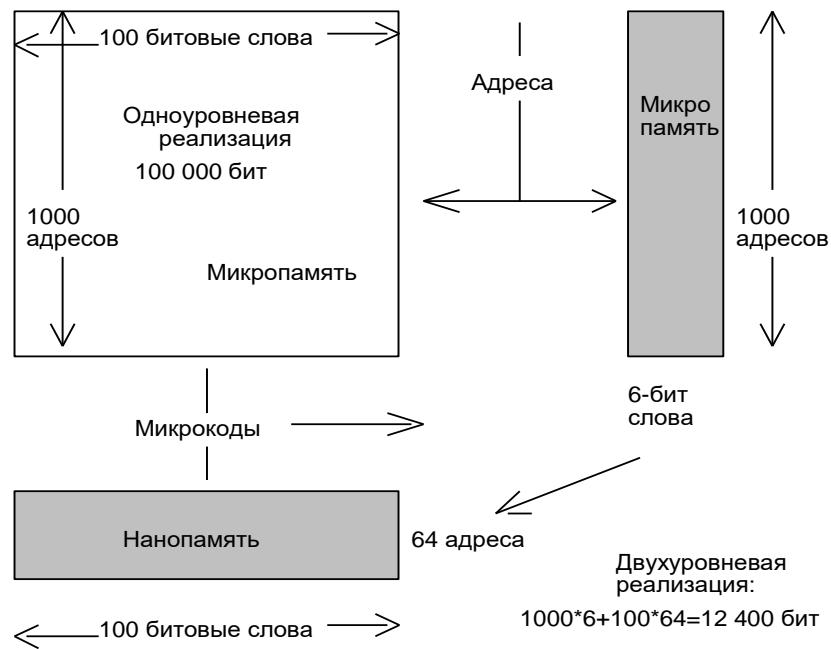

| 3.2. Устройство управления. Микропрограммный автомат. ....                                         | 97  |

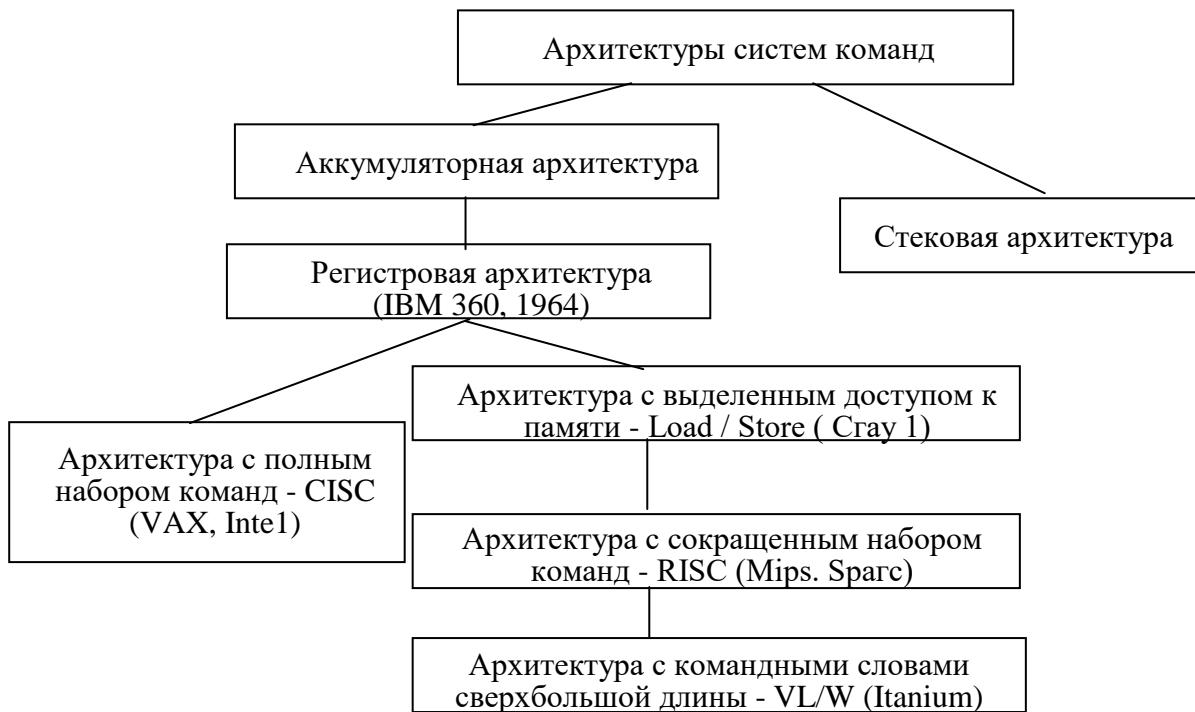

| 3.3. Архитектуры систем команд.....                                                                | 104 |

| 3.4. Ассемблер и система команд процессора на примере процессора Pentium. ....                     | 113 |

| 3.5. Способы адресации.....                                                                        | 124 |

| 3.6. Управление вычислительным процессом .....                                                     | 137 |

| 3.7. AT&T-синтаксис .....                                                                          | 151 |

| 3.8. Ассемблер и макросредства .....                                                               | 152 |

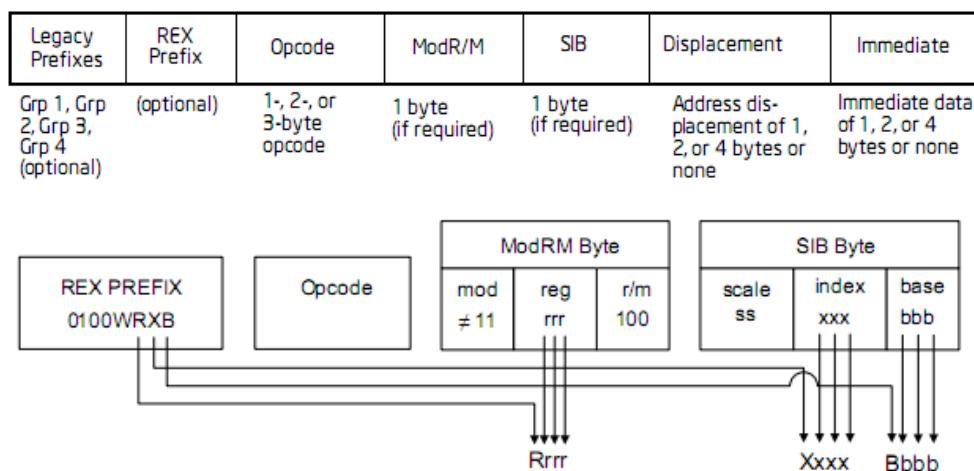

| 3.9. Кодирование команд в процессоре x86.....                                                      | 159 |

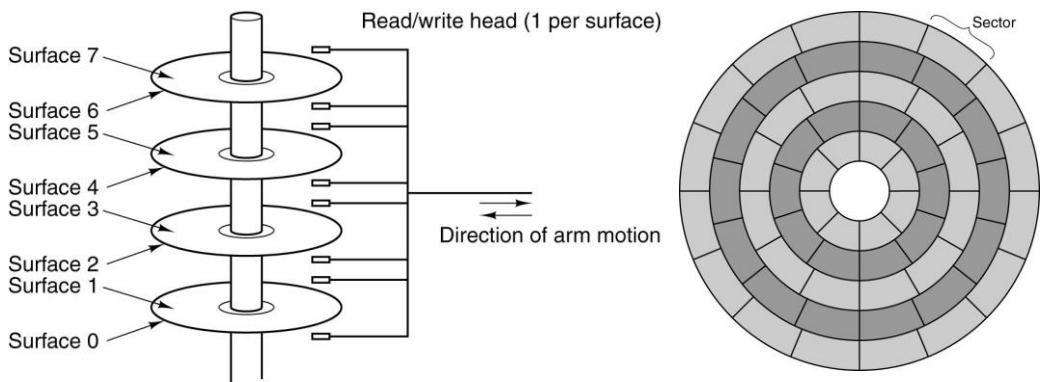

| ГЛАВА 4. ПАМЯТЬ. НИЖНИЙ УРОВЕНЬ .....                                                              | 163 |

| 4.1. Методы доступа.....                                                                           | 163 |

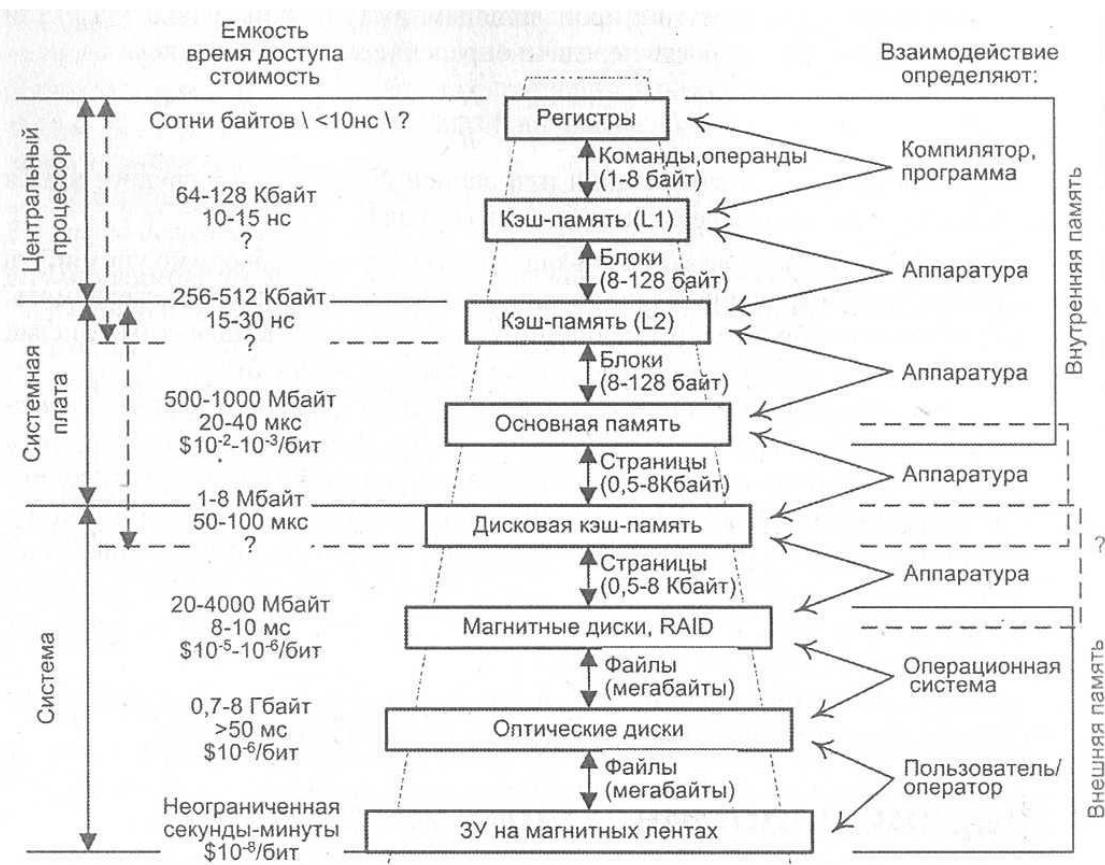

| 4.2. Иерархия запоминающих устройств.....                                                          | 165 |

| 4.3. Основная память. ОЗУ .....                                                                    | 169 |

| 4.4. Микросхемы памяти .....                                                                       | 172 |

| 4.5. Регенерация памяти.....                                                                       | 184 |

| 4.6. Обнаружение и исправление ошибок.....                                                         | 186 |

| 4.7. Флэш-память.....                                                                              | 189 |

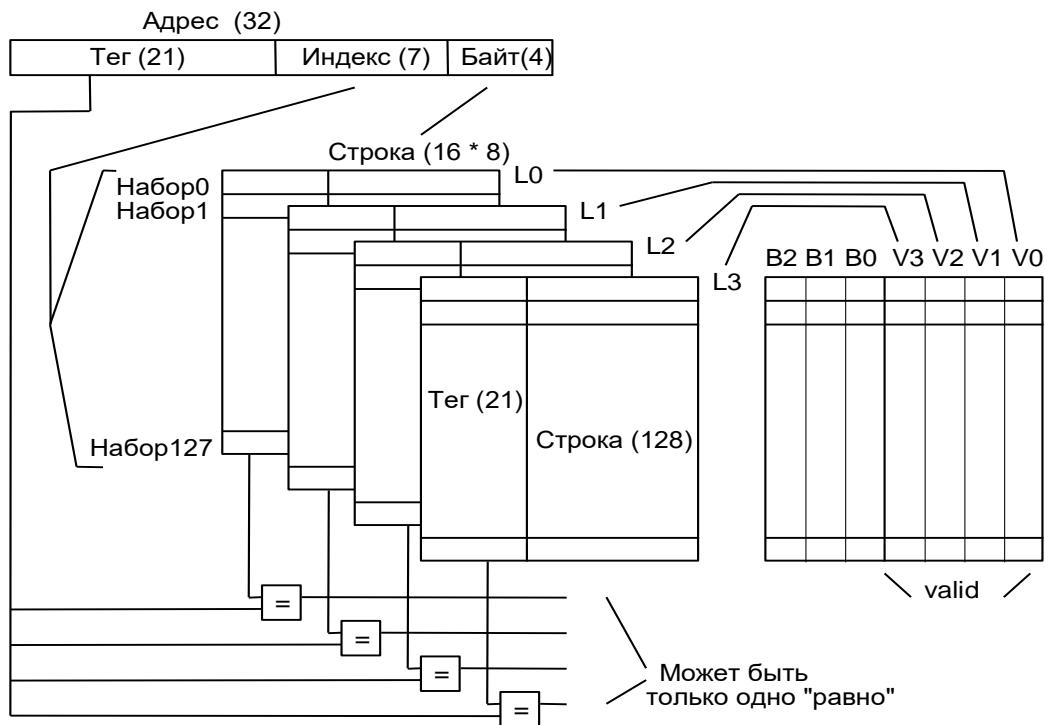

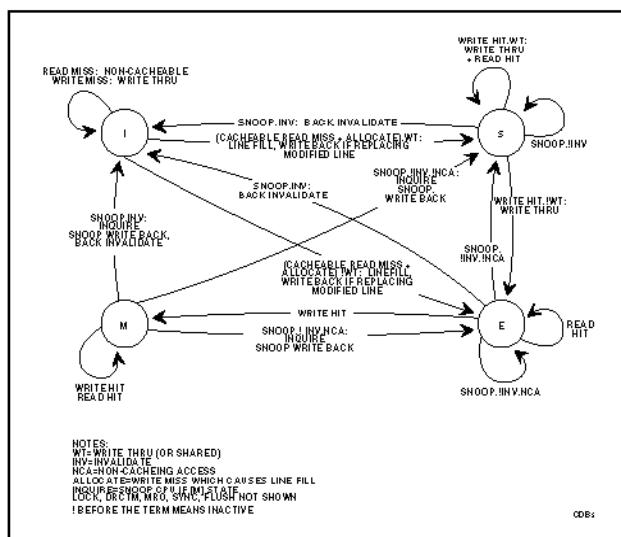

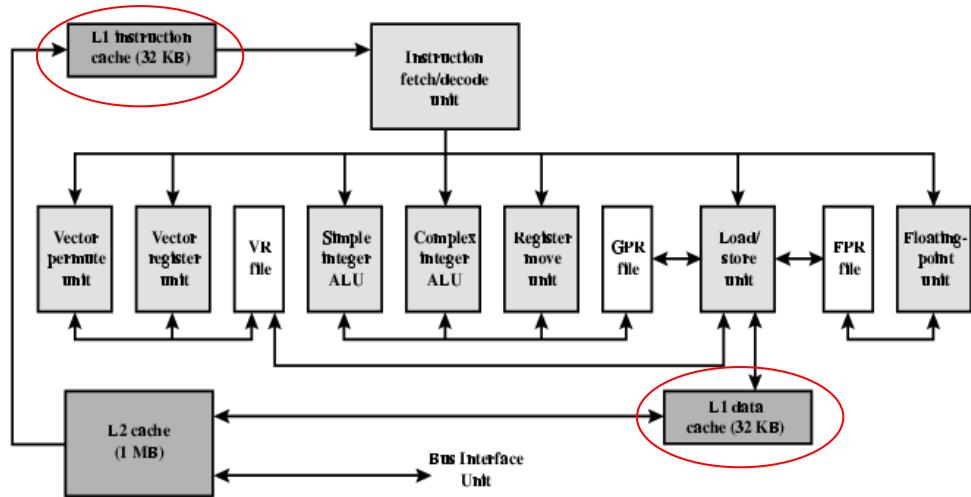

| 4.7. Кэш-память .....                                                                              | 190 |

| 4.8. Многоуровневая кэш-память и пакетный режим передачи данных.....                               | 204 |

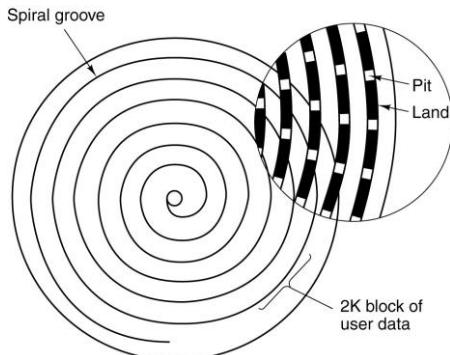

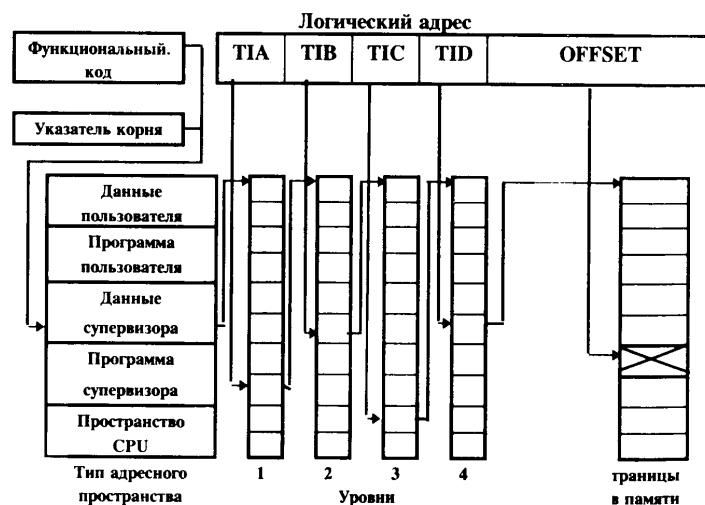

| ГЛАВА 5. ПАМЯТЬ. ВЕРХНИЙ УРОВЕНЬ .....                                                             | 208 |

|                                                                    |     |

|--------------------------------------------------------------------|-----|

| 5.1. Динамическое распределение памяти .....                       | 208 |

| 5.2. Виртуальная память .....                                      | 209 |

| 5.3. Общие принципы защиты памяти.....                             | 215 |

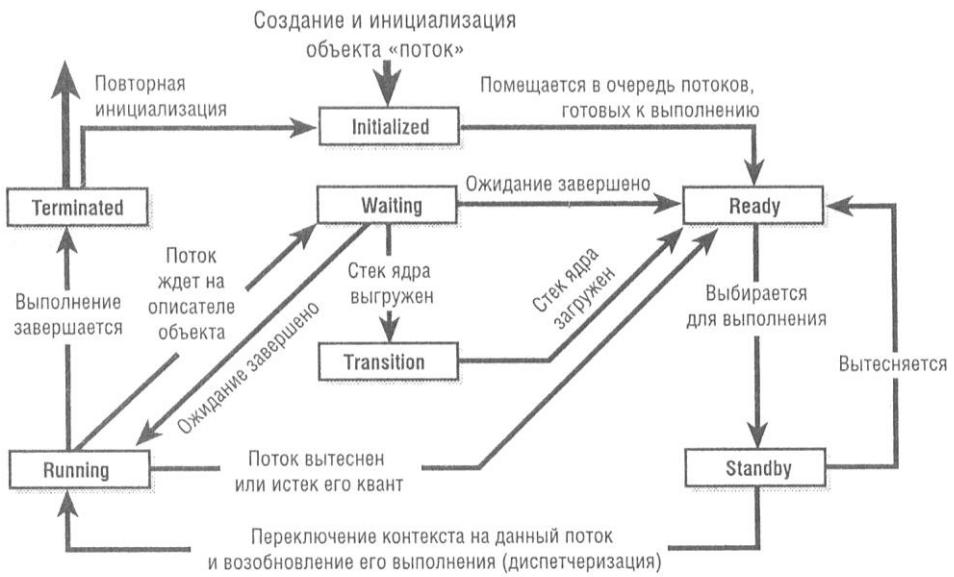

| 5.4. Мультизадачность .....                                        | 217 |

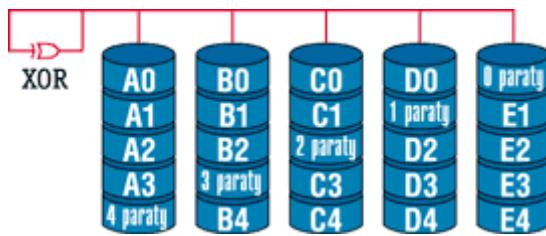

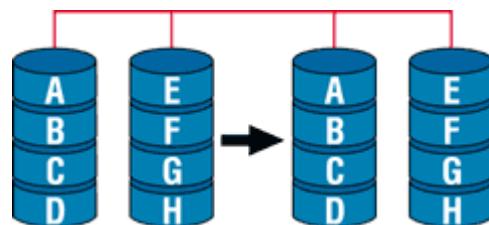

| 5.5. Дисковые массивы и уровни RAID .....                          | 224 |

| 5.6. Организация памяти в процессорах Pentium .....                | 231 |

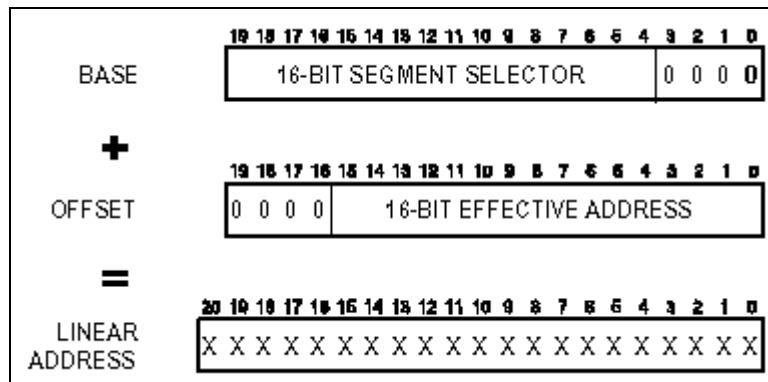

| 5.6.1. Трансляция адреса в реальном режиме.....                    | 232 |

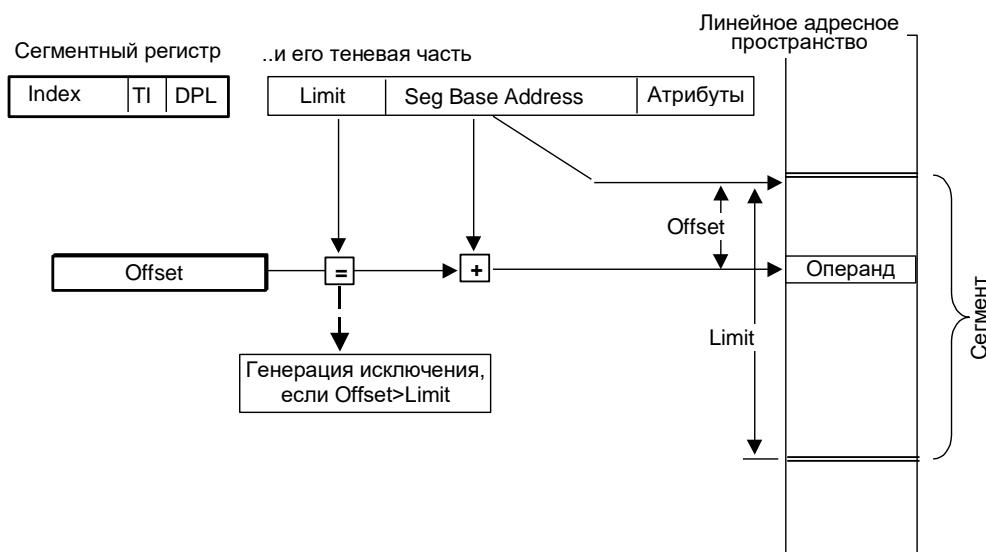

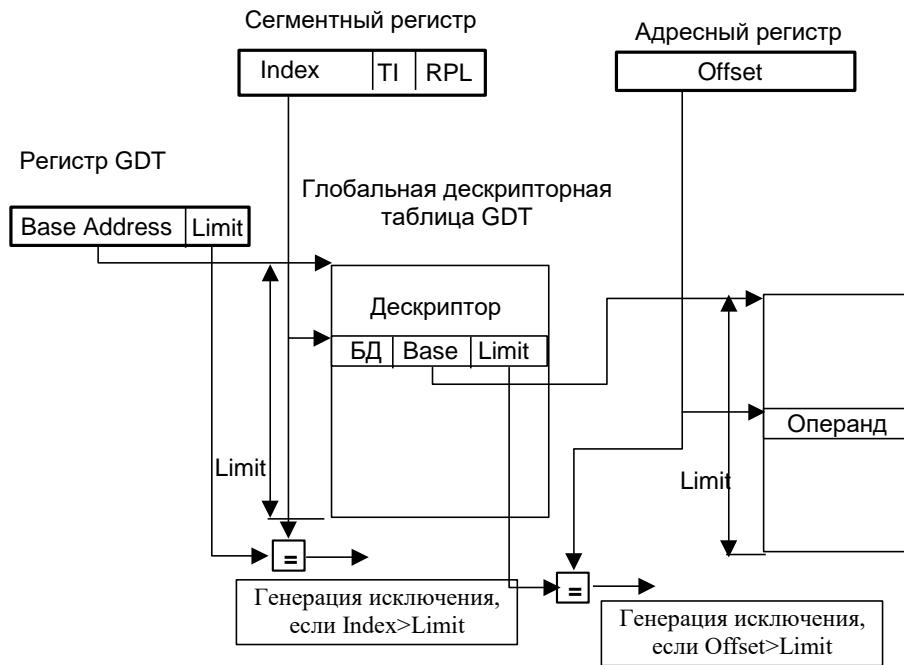

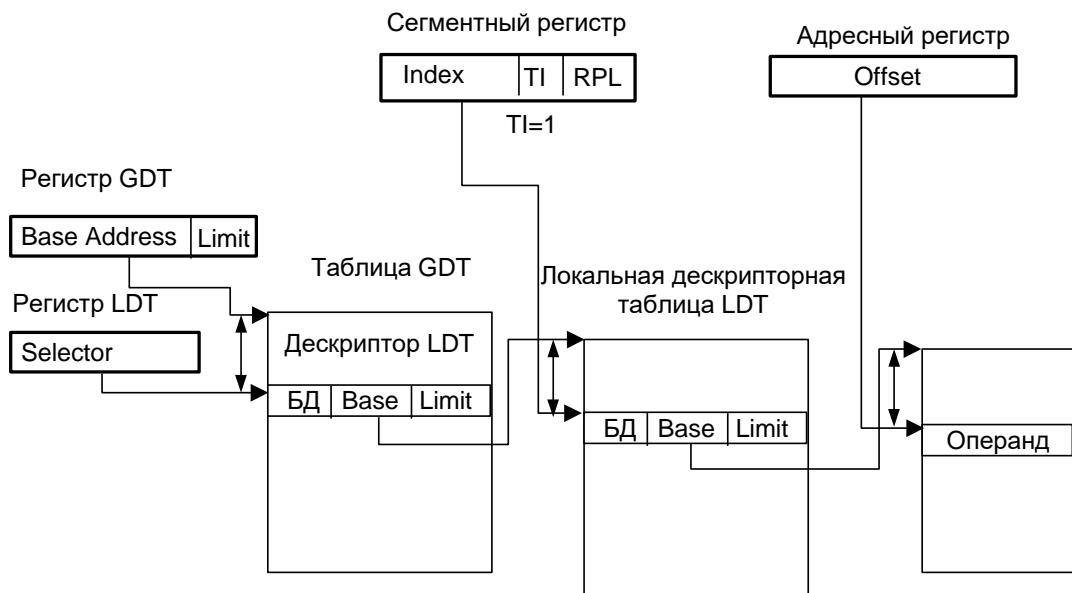

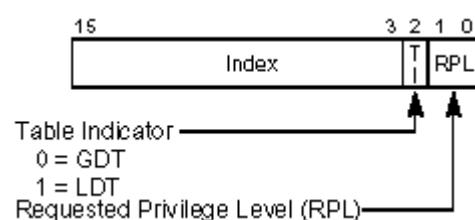

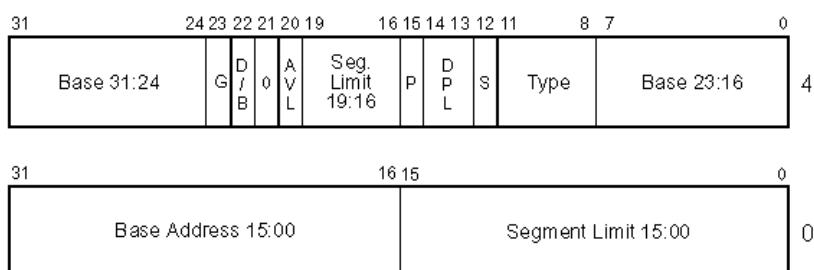

| 5.6.2. Трансляция адреса в защищенном режиме .....                 | 233 |

| 5.6.3. Страницочный механизм.....                                  | 243 |

| 5.6.4. Защита в процессоре Pentium.....                            | 247 |

| 5.6.5. Аппаратная поддержка мультизадачности.....                  | 255 |

| 5.6.6. Прерывания в защищенном режиме .....                        | 260 |

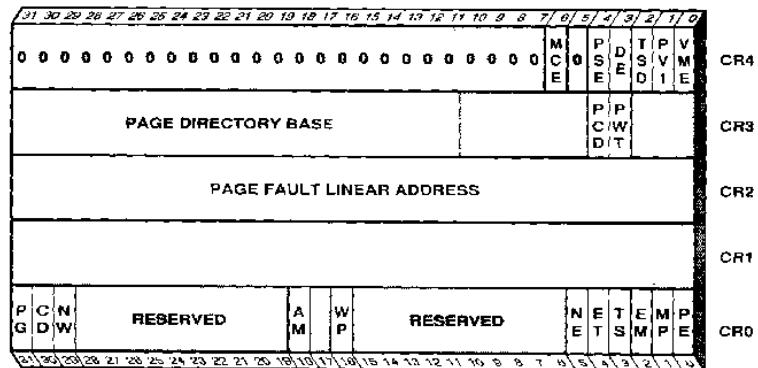

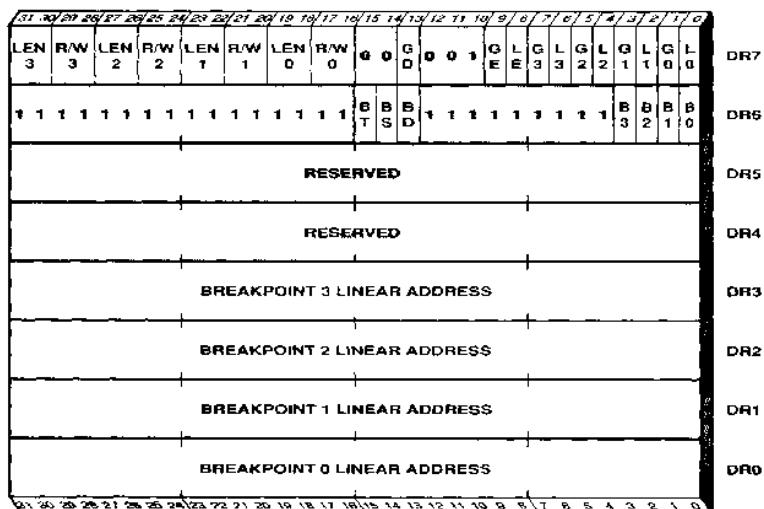

| 5.7. Системные регистры процессоров Pentium .....                  | 263 |

| ГЛАВА 6. ВВОД-ВЫВОД .....                                          | 269 |

| 6.1. Подключение периферийных устройств к ЭВМ .....                | 269 |

| 6.2. Синхронизация выполнения программы с внешними процессами..... | 284 |

| 6.3. Прерывания .....                                              | 287 |

| 6.4. Реализация механизма прерывания в процессорах Pentium .....   | 298 |

| 6.5. Аппаратная поддержка отладки.....                             | 302 |

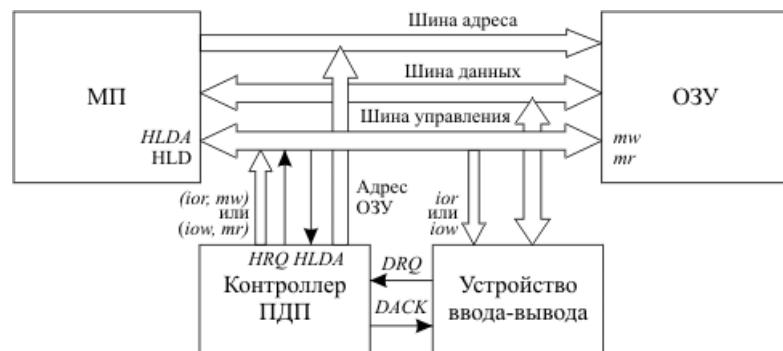

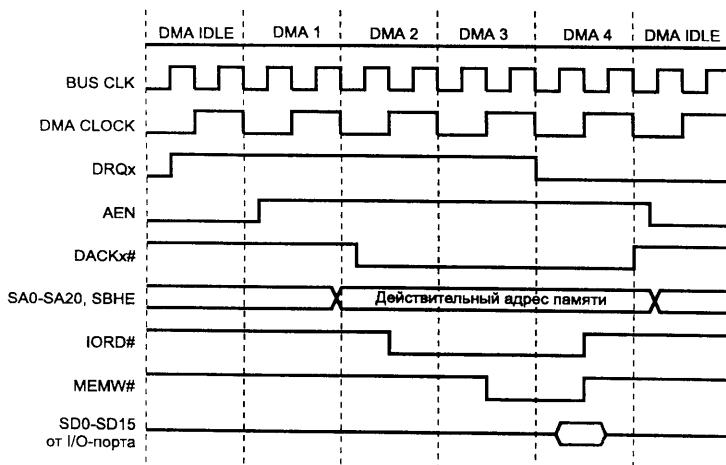

| 6.6. Прямой доступ к памяти.....                                   | 306 |

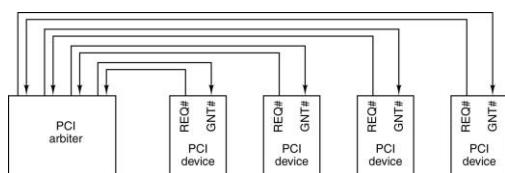

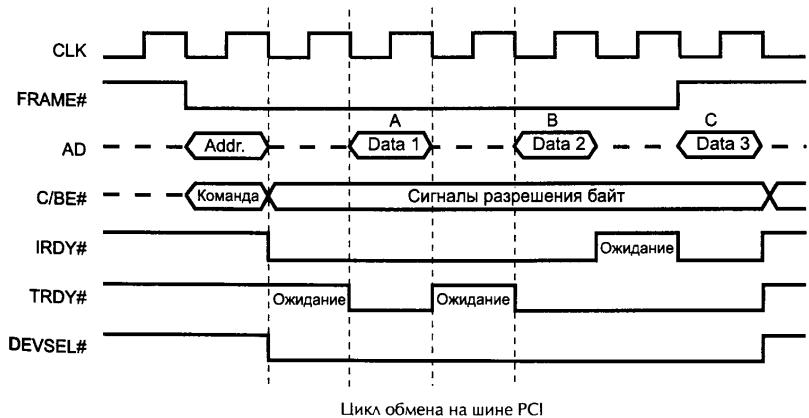

| 6.7. Шины. PCI. PCI Express.....                                   | 311 |

| 6.8. Процесс загрузки компьютера .....                             | 323 |

| Список контрольных вопросов .....                                  | 328 |

| Рекомендуемая литература .....                                     | 331 |

# **ГЛАВА 1. БАЗОВАЯ ОРГАНИЗАЦИЯ ЭВМ**

## **1.1. Многоуровневая организация и эволюция ЭВМ.**

Изучение вычислительной техники и программирования немыслимо без рассмотрения организации ЭВМ. В данном курсе предполагается изучение, как основ функционирования, так и особенностей современных процессоров и периферийных устройств во взаимосвязи с обрабатываемыми видами данных. Рассмотрение проводится как на уровне "модели процессора для программиста", так и на уровне компонентов структурной иерархии, которые не являются впрямую программно-доступными. Рассмотрение аппаратуры неотделимо от программного обеспечения, так как граница между ними постоянно перемещается. Сегодняшнее программное обеспечение может быть завтрашим аппаратным обеспечением и наоборот. Не важно, на каком уровне выполняется команда. Программист, работающий на уровне архитектуры системы, может использовать команду умножения, как будто это команда аппаратного обеспечения, и даже не задумываясь об этом. То, что для одного человека - программное обеспечение, для другого аппаратное.

Развитие компьютерных технологий не останавливается, появляются новые идеи, часть старых забывается. В данном курсе рассматриваются основополагающие подходы к созданию высокопроизводительных процессоров, систем и ЭВМ, делаются непрерывные ссылки на наиболее распространенный в мире компьютер IBM PC.

### **Многоуровневая организация средств цифровой вычислительной техники [10]**

Цифровые вычислительные системы имеют многоуровневую иерархическую организацию, которая проявляется в различных аспектах. В частности, чем ниже работаем - тем больший уровень эффективности доступен, но тем выше трудозатраты при разработке.

Устройство нижележащих уровней может быть скрыто от пользователя, и его для получения практического результата (например, работающего программного продукта) знать не обязательно. Но знание и использование свойств нижележащих уровней позволяет в том или ином смысле повысить эффективность разрабатываемой программы или устройства.

| Уровень                         | Характеристика, примечание                                                                                  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|

| проблемно-ориентированные языки | использование готовой прикладной программы (например, MS Word)                                              |

| процедурно ориент. языки        | программирование прикладной задачи                                                                          |

| уровень языка макроассемблера   | Позволяет поименовать часто повторяющиеся фрагменты кода и в дальнейшем использовать это имя                |

| уровень функций ОС (BIOS)       | Можем пользоваться готовыми типовыми подпрограммами для часто используемых или аппаратно зависимых действий |

| уровень машинных команд         | Если пишем свои аналоги системных функций                                                                   |

| микропрограммный уровень        | Программно невидим, но знание его свойств позволяет улучшать эффективность кода                             |

| уровень аппаратуры              | Доступен во встроенных применениях                                                                          |

При написании оптимизирующих трансляторов, при системном программировании, при разработке приложений, критичных к скорости выполнения, иногда приходится учитывать свойства иерархических уровней, вплоть до аппаратного, для достижения более высокой эффективности. Например, при оптимизации по скорости в процессорах с многопотковыми конвейерами, надо учитывать времена выполнения команд и возможное влияние соседних команд друг на друга.

Сфера нашего рассмотрения - первые 5 уровней.

## **Эволюция развития ЭВМ**

Разные авторы по-разному делят на этапы эволюцию вычислительной техники (ВТ). Мы отметим только ключевые этапы развития электронных вычислительных машин (ЭВМ).

- Нулевое поколение – механическая эра.

Первые счеты – абак в древнем Вавилоне 3000 лет до н.э.

Счеты с косточками на проволоке – Китай 500 лет до н.э.

1492 г. Леонардо да Винчи приводит рисунок тринадцатиразрядного десятичного сумматора на основе **зубчатых колес**.

1642 г. Блез Паскаль изготовил более 10 вычислителей, который суммировали и вычитали пятиразрядные десятичные числа.

1673 г. Г.В.Лейбниц создает вычислитель всех четырех операций над 12-ными десятичными числами. Результат умножения – 16 цифр.

1863 г. Чарльз Бэббидж механическая машина имела считыватель с перфокарт для ввода программ и данных, память (склад) имела объем пятьдесят 40-разрядных чисел и два аккумулятора для хранения промежуточных результатов. Имелись условные переходы. Суммирование занимает 3 с, а умножение 2-4 минуты. Позднее создает принтер.

1885 г. Дорр Фельт – первый калькулятор, в котором числа вводятся нажатием клавиш.

1937 г. Аллан Тьюринг публикует статью, в которой излагает концепцию упрощенной вычислительной машины, получившей название машины Тьюринга.

1938 г. Конрад Цузе – механический программируемый вычислитель Z1 с памятью на 1000 бит. Позднее Z3 с программой на перфоленте. Умнож. 5с.

- Первое поколение – электронные лампы (1945-1955). Типичным представителем является ЭВМ ЭНИАК, которая описана ниже. Это поколение аккумуляторных ЭВМ с небольшой памятью (4 Кбайт).

- Второе поколение – транзисторы (1955-1965). Изобретение транзистора произошло в лаборатории Bell Laboratories, за что получена Нобелевская премия в 1956 г. Появились новые архитектурные элементы: блок обработки чисел с плавающей запятой, общая шина, память на магнитных сердечниках, суперкомпьютеры (Сеймур Крей, суперЭВМ CDC6600 имела быстродействие 1 MFLOPS). Широко распространился отечественный компьютер Минск-32 и миникомпьютер Электроника-100.

- Третье поколение – интегральные схемы (1965-1980). Изобретение кремниевой интегральной схемы в 1958 г. Робертом Нойсом. Архитектурные новшества: конвейерная и параллельная обработка, микропрограммирование, кэш-память, первые операционные системы. Во всем мире широко распространился компьютер IBM-360, который имел следующие характеристики (модель 50): время цикла 500 нс, объем памяти 256 Кбайт, за одно обращение к ОЗУ выбирал 4 байта..

- Четвертое поколение – сверхбольшие интегральные схемы (1980-). Large-scale integration LSI - до 1000 транзисторов на кристалле. Very large-scale integration VLSI - до 100 000 транзисторов на кристалле. Появился микропроцессор – ЭВМ на кристалле, а затем и персональные ЭВМ Intel и Apple. В 1981 году появился первый персональный компьютер IBM PC. Основная память стала полупроводниковой. Идея ЭВМ с сокращенным набором команд – RISC идеология. Язык программирования С.

- Пятое и шестое поколение – мультипроцессорные системы (1990-)

**Закон Мура: Число транзисторов на микросхеме удваивается каждые 18 месяцев.**

Гордон Мур (Gordon Moore) основал компанию Intel вместе с Робертом Нойсом (Robert Noyce) в 1968 году. Сначала Гордон Мур занимал должность исполнительного вице-президента корпорации. В 1975 г. он стал президентом и главным управляющим Intel и оставался генеральным

директором с 1975 по 1987 год. В 1997 г. ему было присвоено звание почетного председателя совета директоров.

Рис. 1.1. Закон Мура. Развитие процессоров Intel.

Свой закон Мур сформулировал в 1965 году, работая над статьей для Electronics magazine (тогда он был сотрудником Fairchild Semiconductor). В то время закон гласил, что число транзисторов на кристалле удваивается каждый год. В 1975 году Мур внес поправку: ...удваивается каждые два года. В 1965 году, в процессе подготовки выступления, Гордон Мур сделал знаменательное наблюдение. Представив в виде графика рост производительности запоминающих микросхем, он обнаружил любопытную закономерность: новые модели микросхем разрабатывались спустя одинаковые периоды - 18-24 месяца - после появления их предшественников, а емкость их при этом возрастала каждый раз примерно вдвое. Если такая тенденция продолжится, заключил Мур, то мощность вычислительных устройств экспоненциально возрастет на протяжении относительно короткого промежутка времени.

Закон постоянно действует и многие считают, что это будет происходить, возможно, до 2020 года. В подтверждении приведем график (рис. 1.1.).

Другие компьютерные «законы»:

**Закон Рока.** Это всего лишь маленькое дополнение к закону Мура: "стоимость основных фондов, используемых в производстве полупроводников, удваивается каждые четыре года".

**Закон Макрона.** Закон Мура лежит в основе закона Макрона, действующего уже на протяжении долгих лет. Закон это гласит: "машина, которая бы вас полностью устроила, никак не может стоить меньше \$5000".

**Первый натановский закон.** (Натан Мирвольд главный администратор компании Microsoft). Программное обеспечение – это газ. Оно распространяется и полностью заполняет резервуар, в котором находится.

## 1.2. Архитектурные принципы Фон-Неймана

В каждой области науки и техники существуют некоторые фундаментальные идеи или принципы, которые определяют ее содержание и развитие. В компьютерной науке роль таких фундаментальных идей сыграли принципы, сформулированные независимо друг от друга - американским математиком и физиком Джоном фон Нейманом и советским ученым Сергеем Лебедевым. (Джон фон Нейман (1903-1957), Сергей Лебедев (1902-1974).) Эти принципы определяют основы организации компьютера.

Считается, что первый электронный компьютер ЭНИАК был изготовлен в США в 1946г. (смотри линейку развития компьютеров) ЭНИАК состоял из 18000 электронных ламп и 1500 реле и весил 30 тонн. Он имел 20 регистров, каждый из которых мог содержать 10-разрядное десятичное число. Блестящий анализ сильных и слабых сторон проекта ЭНИАК был дан в отчете Принстонского института перспективных исследований "Предварительное обсуждение логического конструирования электронного вычислительного устройства" (июнь 1946 г.). Этот отчет, составленный выдающимся американским математиком Джоном фон Нейманом и его коллегами по Принстонскому институту Г. Голдстайном и А. Берксом, представлял проект нового электронного компьютера. Идеи, высказанные в этом отчете, известны под названием "Неймановских Принципов".

Говоря об основоположниках теоретической информатики, нельзя не упомянуть о двух научных достижениях, алгебре логики и теории алгоритмов. Алгебра логики была разработана в середине 19-го века английским математиком Джорджем Булем и рассматривалась им в качестве метода математизации формальной логики. Разработка электронных компьютеров на двухпозиционных электронных элементах создала возможным широкое использование "булевой логики" для проектирования компьютерных схем. В первой половине 30-х годов 20-го столетия появились математические работы, в которых была доказана принципиальная возможность решения с помощью автоматов любой проблемы, поддающейся алгоритмической обработке. Данное доказательство содержалось в опубликованных в 1936 г. работах английского математика А. Тьюринга и американского математика Э. Поста. (Джордж Буль (1815-1864) Алан Тьюринг (1912-1954))

В Советском Союзе работы по созданию электронных компьютеров были начаты несколько позже. Первый советский электронный компьютер был изготовлен в Киеве в 1953г. Он назывался МЭСМ (малая электронная счетная машина), а его главным конструктором был академик Сергей Лебедев, автор проектов компьютеров серии БЭСМ (большая электронная счетная машина). В проекте МЭСМ Сергей Лебедев независимо от Неймана пришел к тем же идеям конструирования электронных компьютеров, что и Нейман.

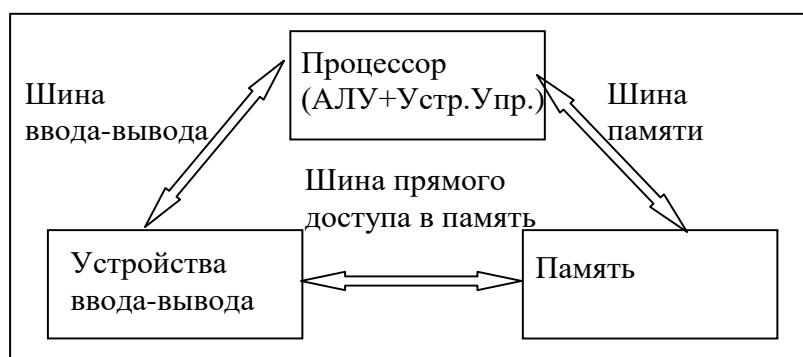

Рис. 1.2. Структурная схема типовой ЭВМ.

Сущность "Неймановских Принципов" состояла в следующем:

1. Компьютер включает связанные между собой Процессор (арифметическое устройство и устройство управления), Память и Устройства ввода-вывода (рис. 1.2).

2. Компьютеры на электронных элементах должны работать не в десятичной, а в двоичной системе счисления.

3. Программа, так же как и числа, с которыми оперирует компьютер, записываются в двоичном коде, то есть по форме представления команды и числа однотипны.

4. Программа должна размещаться в одном из блоков компьютера - в запоминающем устройстве, которое имеет произвольный доступ. Программа и данные могут находиться в общей памяти (принстонская архитектура).

5. Трудности физической реализации запоминающего устройства большого быстродействия, энергонезависимого и большой памяти требуют иерархической организации памяти. Программа выполняется из основной памяти, а сохраняется в энергонезависимой вторичной памяти (магнитных дисках). Файл – идентификационная совокупность экземпляров полностью описанного в конкретной программе типа данных, находящихся вне программы во внешней памяти и доступных программе посредством специальных операций (согласно стандарту ISO).

6. Арифметико-логическое устройство (АЛУ) компьютера конструируется на основе схем, выполняющих операцию сложения, сдвига, логическую операцию. Помимо результата операции АЛУ формирует ряд признаков результата (флагов), которые могут анализироваться при выполнении команд условной передачи управления.

7. В компьютере используется параллельный принцип организации вычислительного процесса (операции над двоичными кодами осуществляются одновременно над всеми разрядами).

8. Централизованное последовательное управление при выполнении команд. Нет конвейера, параллельности, внеочередного выполнения и прочего, что свойственно современным процессорам.

9. Линейная структура адресации памяти.

10. Низкий уровень машинного языка. Нет микропрограммируемости.

Существенно подчеркнуть, что центральное место среди "принципов Неймана" занимает предложение об использовании двоичной системы счисления, что было обусловлено рядом обстоятельств. Во-первых, несомненными арифметическими достоинствами двоичной системы счисления, ее "оптимальным" согласованием с "булевой" логикой и простотой технической реализации двоичного элемента памяти (триггера).

### **Выполнение команд по программе, хранимой в ЭВМ.**

Программа представляет собой последовательность команд, хранимых в памяти компьютера. Команды в ЭВМ (в машине фон Неймана) располагаются в ячейках программной памяти подряд, одна за другой. Процессор по порядку считывает команды из памяти и выполняет их. Этот процесс сводится к последовательному выполнению этапов: считывание команды из памяти, дешифрация команды, обращение к памяти за операндом, выборка операнда, исполнение операции, запись результата в память. Операнд или результат могут быть взяты/записаны в устройства ввода-вывода. Следующая команда выполняется после завершения предыдущей команды. Ее адрес содержится в особом регистре процессора, называемом указателем (или счетчиком) команд. После считывания очередной команды процессор автоматически увеличивает содержимое счетчика команд, так, что он указывает на следующую команду.

Известны альтернативные пути построения компьютера:

- Потоковая машина – действиями управляют сами данные.

- Нейронные сети и др.

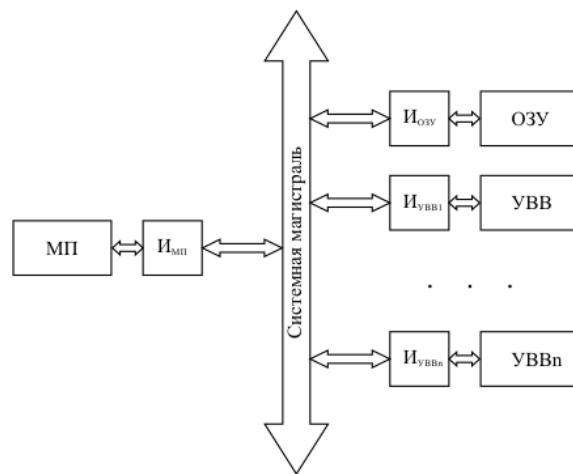

### **1.3. Магистральная вычислительная структура**

Принципы фон Неймана применимы и к магистральной или шинной архитектуре. В этом случае ЭВМ включает четвертый элемент – магистраль, которая связывает отдельные элементы и влияет на выполнение команд.

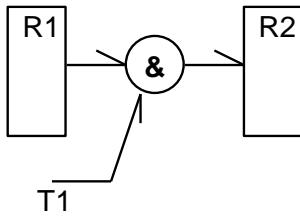

**Магистраль/канал** – унифицированная подсистема связи структурных частей ЭВМ. Унификация магистрали состоит в том, что все устройства подключаются к магистрали одинаково (используют один и тот же набор сигналов, один и тот же алгоритм обмена). Унификация позволяет легко заменять, добавлять или удалять отдельные части, входящие в состав ЭВМ, без нарушения ее работоспособности. Основные конструктивные компоненты магистрали – линии связи (проводы), которые можно подразделить на три группы (шины) – *адреса, данных и управления*.

**Линии связи** – провод, по которому передается логический сигнал.

**Шина** – группа линий однотипных сигналов.

**Шина адреса** предназначена для передачи из процессора в память параллельным кодом двоичного слова, представляющего собой начальный адрес участка памяти, к которому требуется обращение. Количество линий (ширина шины адреса) определяет *размер физического адресного пространства*, т.е. максимальное количество различных адресов в ОЗУ. Адрес по шине передается от процессора в память или во внешнее устройство. В процессор адрес передается только в мультипроцессорных системах, для поддержания правильной работы КЭШей.

**Шина данных** предназначена для передачи команд и данных между процессором, памятью и периферийными устройствами. Передача слов осуществляется также параллельным кодом, а «ширина» шины данных в реальных системах может составлять от 1 до 4 и более байтов. Шина данных является двунаправленной и имеет наибольшую пропускную способность.

В некоторых ЭВМ шина адреса и шина данных объединены в одну мультиплексируемую шину адреса/данных. Такая шина функционирует в режиме разделения времени: цикл шины разбит на временной интервал передачи адреса и на временной интервал передачи данных. Мультиплексирование позволяет сократить общее число линий, но требует усложнения логики связи с шиной. Кроме того, оно может привести к потере производительности.

**Шина управления** предназначена для передачи управляющих сигналов из процессора в прочие устройства, подключенные к магистрали.

Любое устройство, подключенное к магистрали, должно быть способно:

- а) распознать «свой адрес», формируемый процессором на адреснойшине;

- б) распознать по сигналам на шине управления действие, которого ждет от устройства процессор;

- в) выполнить это действие: передать в процессор либо принять из процессора через шину данных двоичное слово.

Последовательность трех перечисленных шагов составляет «цикл магистрали» (**«канальный цикл»**). Канальные циклы могут следовать на магистрали непрерывно, либо с интервалами. Они происходят под управлением процессора или внешних устройств, и, таким образом, обеспечивают обмен информацией между частями ЭВМ.

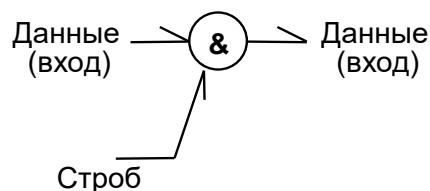

### **Канальный цикл обмена данными.**

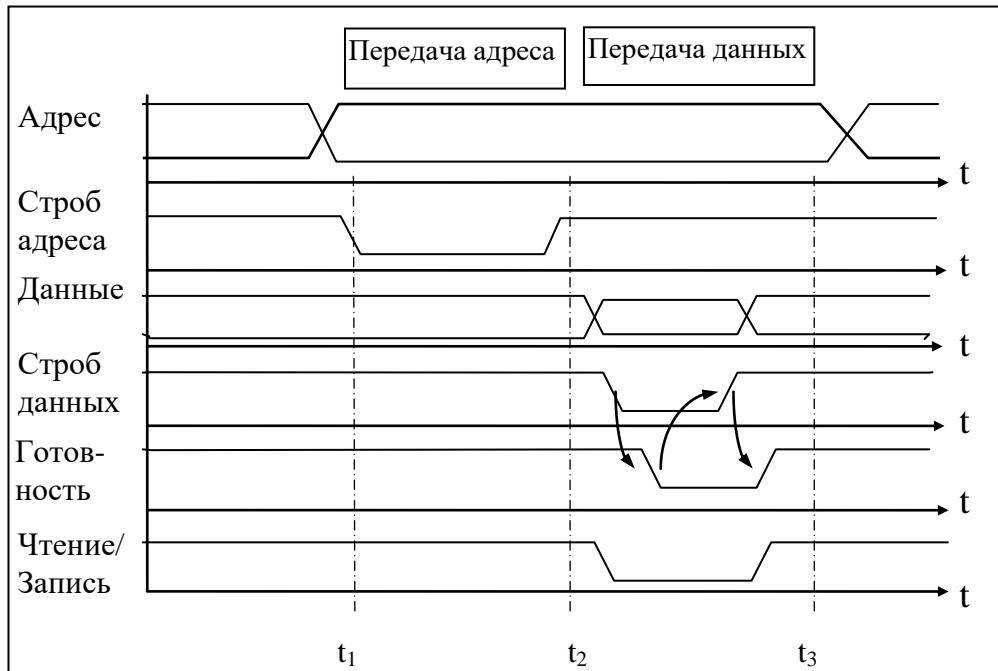

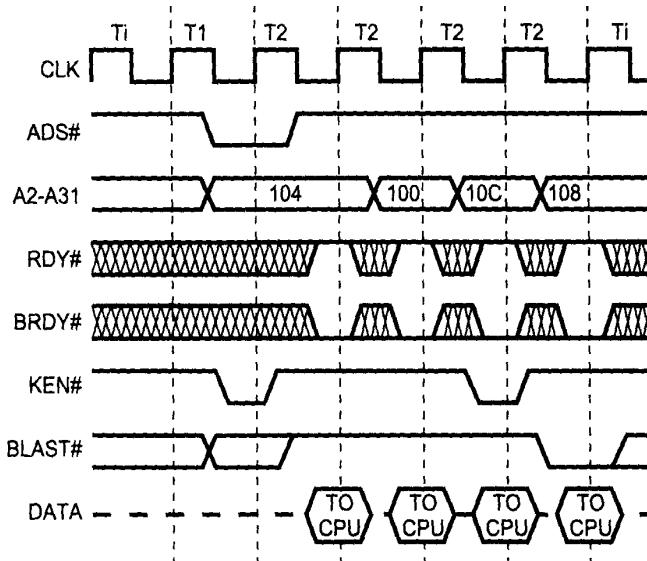

Типовая структура (временная диаграмма) канального цикла обмена данными изображена на рис.1.3. В ней можно выделить два этапа - этап передачи/декодирования адреса – фазу адреса (задается положением во времени строба адреса) и этап передачи данных – фазу данных (задается положением строба данных).

Рис. 1.3. Типовая временная диаграмма канального цикла

для раздельных шин адреса и данных.

**Синхронный канал** - время канального цикла постоянно, адрес/данные записываются синхронно со стробом. Обычно переключение сигналов шины происходит по импульсам тактовой частоты.

**Асинхронный канал** - время канального цикла зависит от приемного устройства, которое после записи данных вырабатывает сигнал Готовности.

В приведенном примере шины адреса и данных - раздельные, адрес передается синхронно, в то время как передача данных производится асинхронно - длительность этапа передачи данных определяется задержкой снятия сигнала Готовности.

**Арбитраж шин.** При любой передаче по шине всегда имеется инициатор передачи или ведущее устройство и имеется приемник данных или ведомое устройство. Ведущее устройство захватывает шину и начинает формировать временную диаграмму ее работы. Если несколько устройств претендуют на права ведущего, то должен быть механизм выбора одного из них. Этот механизм и называется арбитражем шин. Арбитраж построен на основе нескольких положений:

- Каждому из претендентов на шину присваивается определенный уровень приоритета, который может оставаться неизменным (статический приоритет) или изменяться по какому-то алгоритму (динамический приоритет). Шина отдается устройству с наивысшим приоритетом.

- Может использоваться централизованная схема арбитража или децентрализованная. Центральный арбитр, находящийся, например, в контроллере шины, принимает запросы параллельно или последовательно от устройств и решает задачу предоставления шины. В децентрализованной схеме каждый ведущий может иметь контроллер шины и самостоятельно принимать решение о ее захвате.

- Ограничение времени управления шиной. Вне зависимости от модели арбитража должно быть предусмотрено ограничение времени управления шиной. Может использоваться несколько вариантов. Например, алгоритм фиксированного кванта времени, который отводится каждому ведущему для захвата шины.

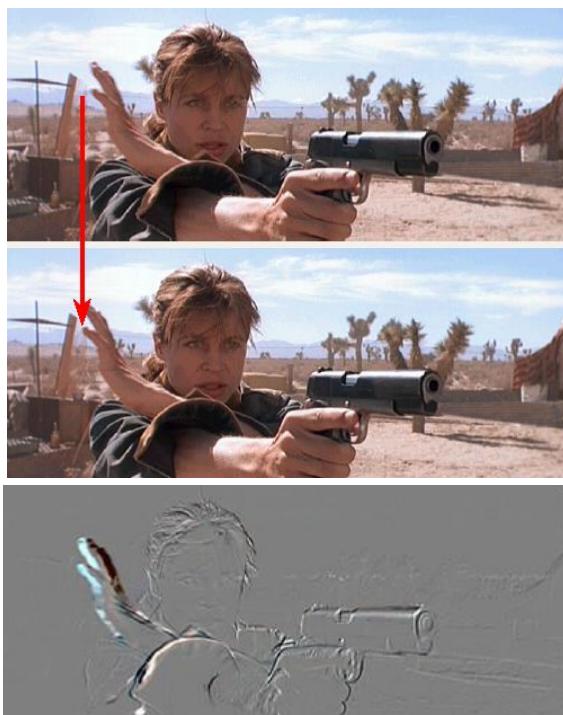

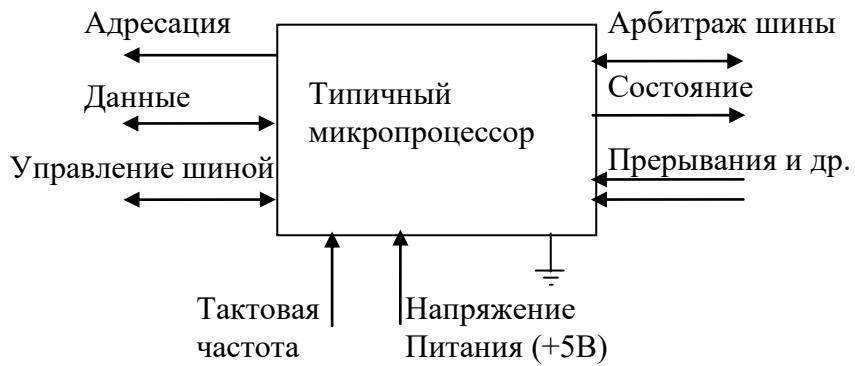

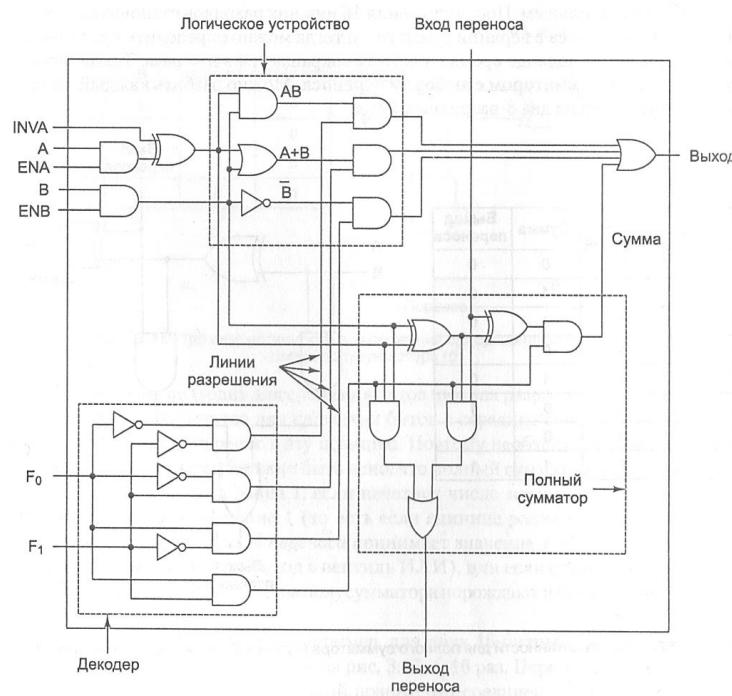

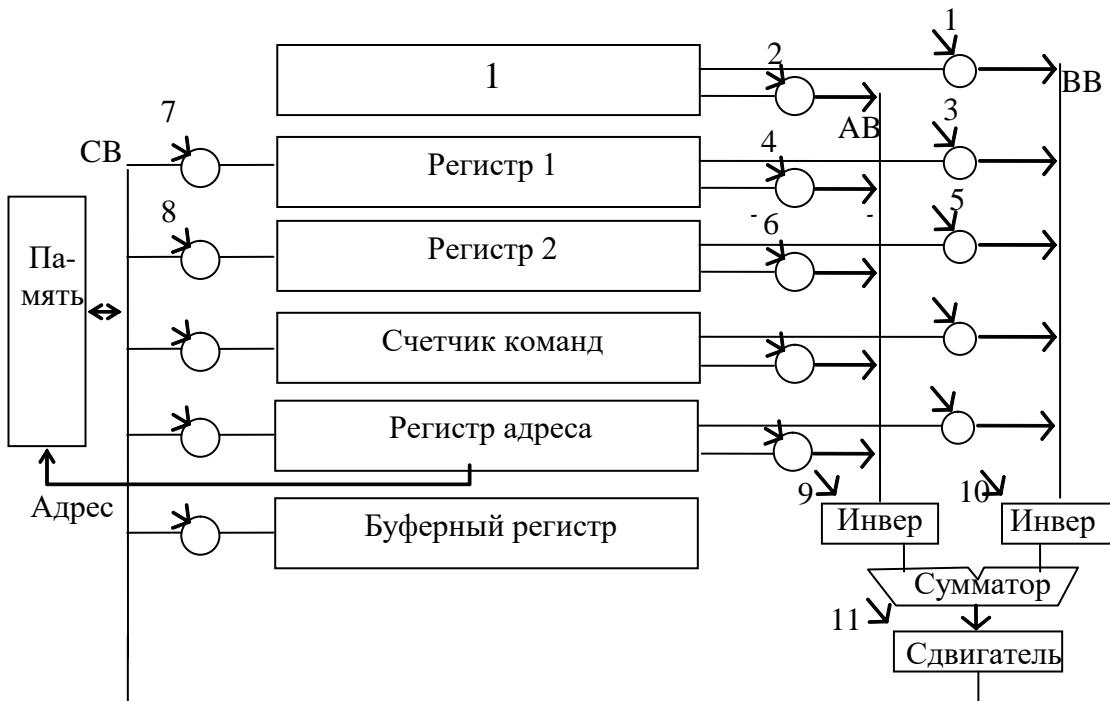

#### **1.4. Процессор. Основные компоненты и их назначение.**

(Central Processor Unit, CPU)

Осуществляет основные действия по выполнению команд. В нем можно выделить несколько составляющих частей:

- 1) декодер команд,

- 2) арифметико-логическое устройство АЛУ, выполняющее действия над операндами,

- 3) регистры для хранения данных, адресов и служебной информации,

- 4) устройство для формирования (вычисления) адресов operandов,

- 5) устройство управления.

**Устройство управления** – управляет процессом последовательной выборки, декодирования и исполнения команд программы, хранимой в памяти. Устройство управления формирует временную диаграмму работы всех узлов процессора. Часть регистров также можно отнести к устройству управления.

**Устройство формирования адресов операндов** – вычисляет адрес, по которому произойдет очередное обращение к участку памяти, содержащему operand.

**АЛУ** – комбинационное логическое устройство, имеющее два (многоразрядных) входа (на которые подаются два слова входных operandов), на выходе АЛУ формируется результат операций, которые процессор выполняет над *operandами*, таких, как сложение, умножение и т.п. Минимальный набор операций (машина Фон Неймана), которые должно выполнять АЛУ, включает операции сложения, инверсии и логического «И», все остальные операции можно получить на базе этих.

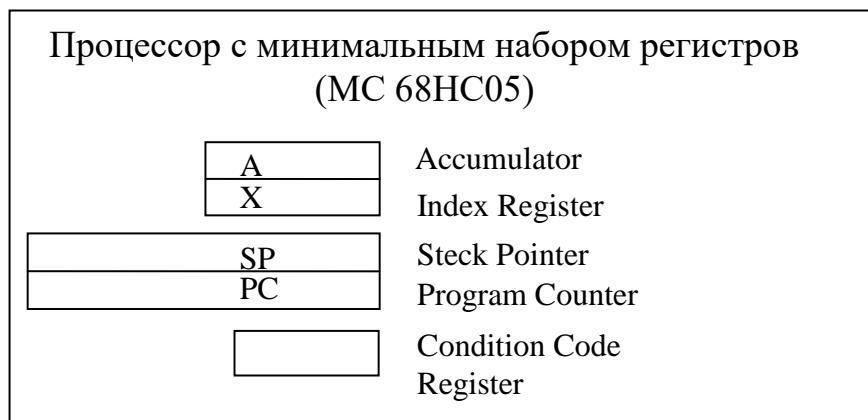

**Регистры.** Минимальный набор регистров, необходимый для функционирования процессора включает следующие регистры:

*аккумулятор* – хранит результаты операций, часто имеет удвоенную длину по сравнению с разрядностью процессора (для хранения результатов операций умножения и сдвига);

*счетчик команд* – содержит адрес следующей команды;

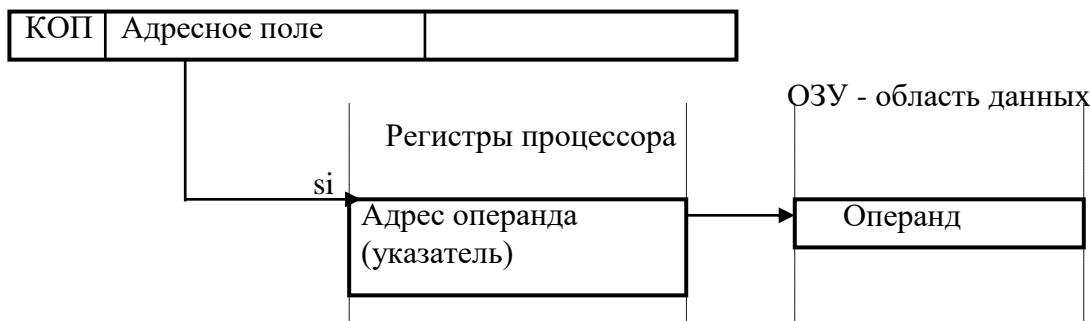

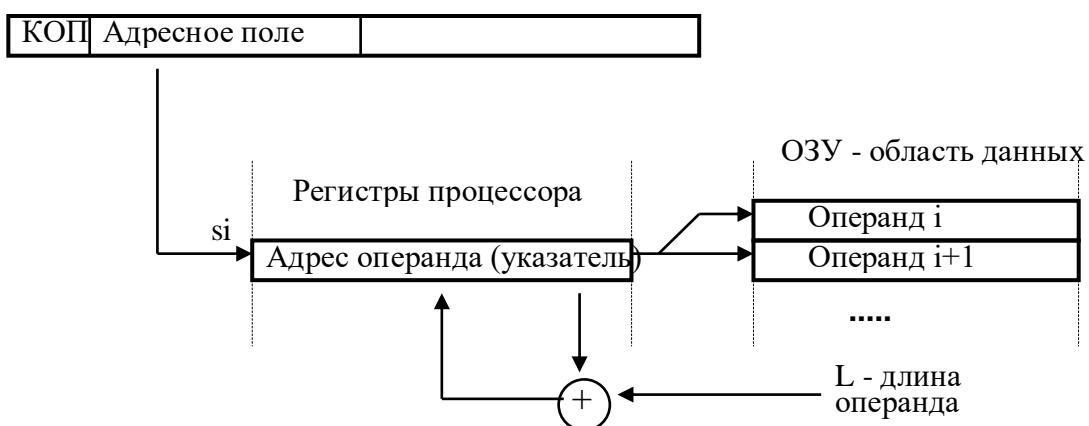

*регистр адреса* – содержит адрес operand, используется при косвенной адресации;

*регистр флагов* (состояния и управления) - содержит код, характеризующий результаты предыдущих операций, а также информацию о текущем состоянии процессора.

Рис. 1.4. Регистры процессора MC68HC05

*Регистровый файл* - набор однотипных регистров.

Каждый процессор имеет свой набор регистров. Так процессор – микроконтроллер МС68HC05 (рис. 1.4) имеет минимально возможный набор регистров. Можно выделить две большие группы процессоров: с *регистрами общего назначения* (регистровыми файлами) и со *специализированным набором регистров* (рис. 1.5). В первом случае все регистры регистрарного файла одинаковы и их можно использовать произвольно в командах (упрощается программирование). Во втором случае за каждым регистром закреплена своя функция, и использование регистров в командах оговорено в формате каждой команды. Однако процессоры с регистровыми файлами требуется большие аппаратные затраты на организацию связи между регистрами. Так процессоры Motorola 68020 состояли из двух микросхем, в то время как процессоры Intel80386 только из одной.

*Модель процессора для программиста* – набор регистров, форматы команд, способы адресации, организация памяти и др. Можно рассматривать регистровую модель процессора - набор регистров, их форматы и способы работы с ними.

- на пользовательском уровне (регистры общего назначения и флагов)

- на системном уровне (регистры управления процессором и организации памяти, элементы организации прерываний и прямого доступа к памяти)

*Вычислительное ядро* (Core) – этим термином обозначают совокупность элементов процессора, необходимых для выполнения команды.

*Периферийные устройства* – устройства, внешние по отношению к связке процессор - память.

*Устройства ввода-вывода* – часть периферийных устройств, предназначенная для связи ЭВМ с «внешним миром». (Прочие периферийные устройства обслуживают внутренние потребности ЭВМ: таймеры, контроллер прерываний,...).

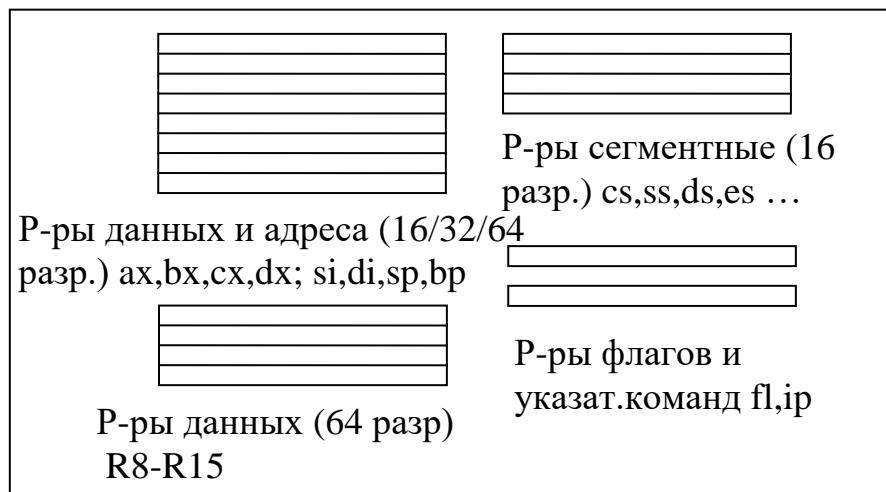

## 1.5. Программная модель процессора Pentium.

Под программной моделью на пользовательском уровне процессора Pentium мы будем понимать всю линейку процессоров IntelXX86 от 16-ти до 64-х разрядных процессоров. Программисту на уровне команд доступны четырнадцать регистров (рис. 1.5). Их удобно разбить на четыре группы: 1)Регистры данных, 2)адресные, 3)сегментные 4)указатель команд и регистр флагов (признаков). Для 64-х разрядных процессоров имеется еще одна группа из 8-ми регистров данных.

Рис. 1.5. Регистры процессора Pentium на пользовательском уровне.

- 1) Регистры данных (в некоторых книгах их называют регистрами общего назначения). Операнды в этих регистрах могут быть как слова, так и байты. Если операнд - байт, может быть указана любая половина регистра. Есть ряд команд, в которых функции отдельных регистров специализированы.

- 2) Указатели и индексные регистры (адресные регистры, используются для хранения 16-разрядных адресов).

- 3) Сегментные регистры (указывают начала четырех сегментов - участков по 64 К байт в 1М ОЗУ: сегмент команд CS, сегмент стека SS и два сегмента данных - DS и ES extra)

- 4) Указатель команд и регистр флагов.

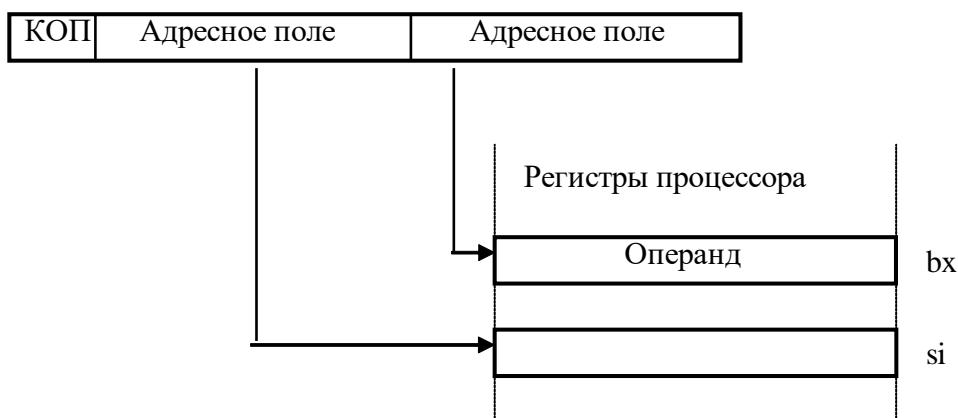

### Функции регистров i8086

|                            |                                                      |

|----------------------------|------------------------------------------------------|

| <b>AX Аккумулятор</b>      | Умножение, деление и ввод-вывод слов                 |

| <b>AL Аккумулятор(мл)</b>  | Умножение, деление и ввод-вывод байтов               |

| <b>AH Аккумулятор(ст)</b>  | Умножение и деление байтов                           |

| <b>BX Регистр базы</b>     | Базовый регистр, может быть использован как адресный |

| <b>CX Счетчик</b>          | Операции с цепочками, циклы                          |

| <b>CL Счетчик (мл)</b>     | Динамические сдвиги и ротации                        |

| <b>DX Данные</b>           | Умножение и деление слов, косвенный ввод-вывод       |

| <b>SP Указатель стека</b>  | Стековые операции                                    |

| <b>BP Указатель базы</b>   | Базовый регистр                                      |

| <b>SI Индекс источника</b> | Операции с цепочками, индексный регистр              |

| <b>DI Индекс приемника</b> | Операции с цепочками,                                |

Примеры команд с регистрами:

|            |             |

|------------|-------------|

| mov ax,bx; | ax = bx     |

| add ax,dx; | ax= ax + dx |

Примеры команд с 8-ми, 16-ти, 32-х, 64-х разрядными регистрами:

add al,cl // add ax,cx // add eax,ecx // add rax,rcx

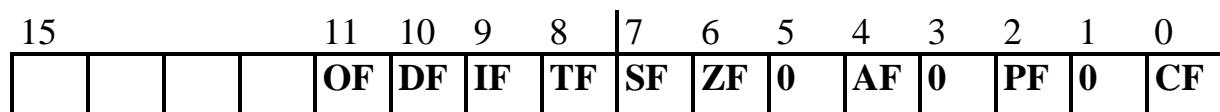

### Регистр флагов процессора i8086

CF ( Carry Flag ) - флаг переноса;

PF ( Parity Flag ) - флаг четности;

AF ( Auxiliary Carry Flag ) - флаг вспомогательного переноса;

ZF ( Zero Flag ) - флаг нуля;

SF ( Sign Flag ) - флаг знака;

TF ( Trap Flag ) - флаг прерывания для отладки

IF ( Interrupt-Enable Flag ) - флаг разрешения прерывания;

DF ( Direction Flag ) - флаг направления цепочечных команд

OF ( Overflow Flag ) - флаг переполнения.

### Сегментные регистры и организация памяти.

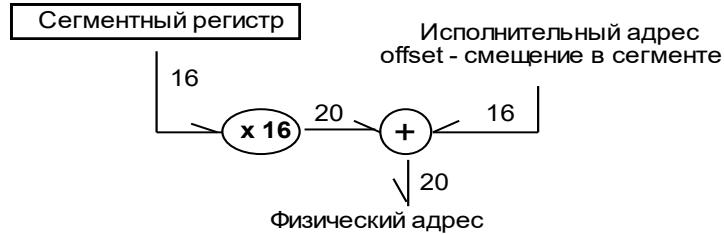

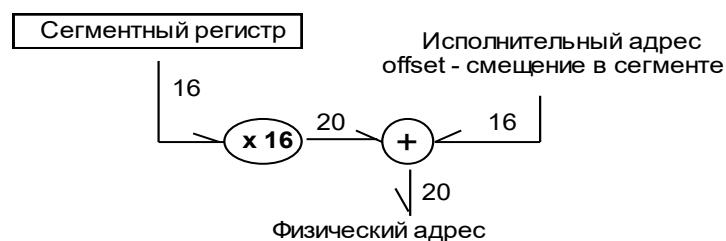

Для формирования физических адресов используется механизм сегментации памяти. Необходимость сегментной организации памяти

определяется недостаточным размером адресных регистров для адресации к памяти большей 64 Кбайт. Для организации адресации в процессоре используются четыре (в i80386 и выше шесть) 16-разрядных сегментных регистра, которые указывают на начала четырех сегментов памяти - участков по 64 К байт: сегмент команд CS, сегмент стека SS и два сегмента данных - DS и ES extra). Местоположение операнда в сегменте определяется смещением (offset).

Адресуемая память (адресное пространство для i8086) представляет собой область из 1М байт. Два смежных байта образуют слово. Адресом слова считается адрес младшего байта. Физический адрес памяти имеет длину 20 бит, однако, все обрабатываемые в регистрах процессора величины имеют длину 16 бит. Схема трансляции приведена на рис.1.6.

Рис. 1.6. Вычисление физического адреса в процессоре Intel X86.

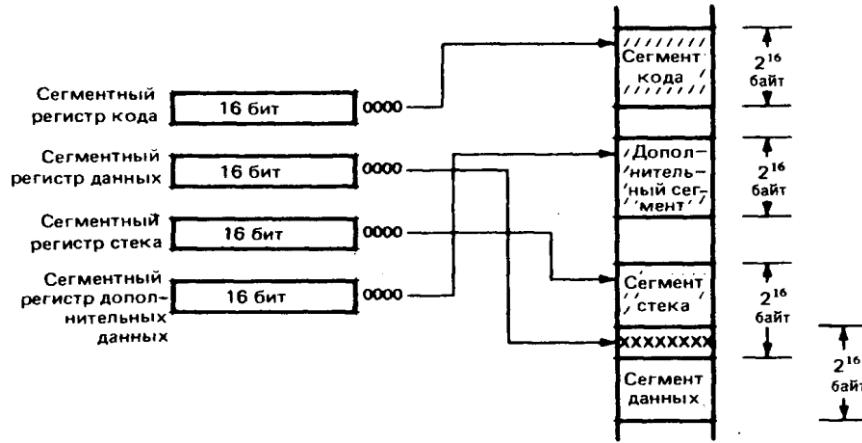

Как было уже сказано, пространство памяти 1 М доступно процессору через 4 "окна" (сегмента). Начальный адрес каждого сегмента содержится в одном из четырех сегментных регистров (рис.1.7). Команды обращаются к байтам и словам в пределах сегментов, используя относительный (внутрисегментный) адрес. Таким образом, адрес операнда задается двумя компонентами: адресом сегмента и смещением. Адрес сквозной нумерации 0xb8000 задается в виде: **0xb800:0**.

Рис. 1.7. Сегментная организация памяти в процессоре Intel X86.

## 1.6. Оперативная память (общая характеристика)

**Оперативная память** (оперативное запоминающее устройство ОЗУ) – часть компьютера, которая хранит команды выполняемых программ и элементы обрабатываемых данных и тесно взаимодействует с процессором в ходе выполнения программы.

Часть памяти, непосредственно взаимодействующая с процессором, имеет организацию с произвольным доступом. Эту часть называют *оперативной памятью* (*оперативным запоминающим устройством ОЗУ*). Этому термину почти соответствует английский эквивалент *Random Access Memory RAM*.

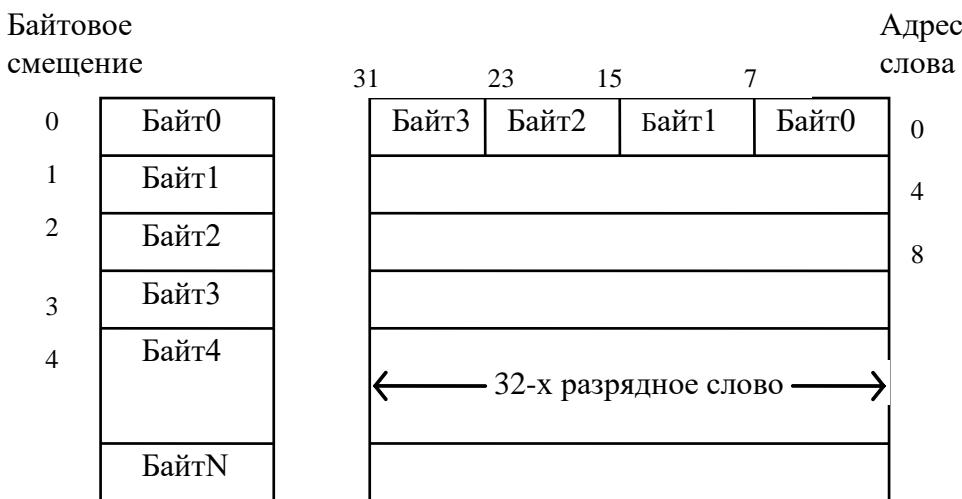

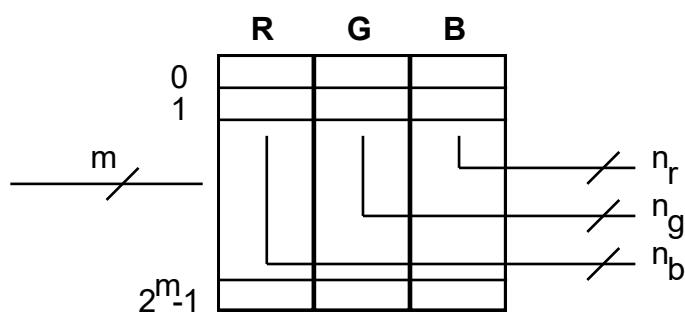

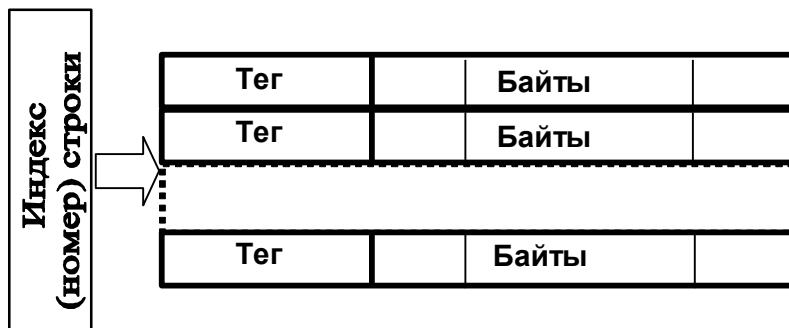

Структурно физически реализованное устройство ОЗУ представляет собой (одномерный) упорядоченный массив запоминающих ячеек одинаковой разрядности (рис. 1.8), которые далее будем называть *минимальными адресуемыми единицами (MAE)*. Разрядность MAE в большинстве компьютеров в настоящее время равна одному байту (8 битов), хотя и сегодня есть модели, в которых адресуемая единица памяти имеет другую длину.

Рис. 1.8. Схема побайтной организации памяти.

Если команды и данные хранятся в одном и том же ОЗУ, такую архитектуру называют *принстонской* (машина Фон-Неймана).

Если команды и данные хранятся в разной памяти, такую архитектуру ЭВМ называют *гарвардской*.

Ячейки физической памяти пронумерованы подряд. Номер ячейки физической памяти называют ее *физическим адресом*. Длина команды или элемента данных (операнда) нередко превышает длину МАЕ. Таким образом, каждый элемент программы (команда) или данных (операнд) хранится в ОЗУ, начиная с определенного адреса, и занимает там одну или несколько МАЕ. Когда говорят об адресе команды или об адресе элемента данных, имеют в виду адрес младшей МАЕ.

Большинство процессоров способно оперировать с двоичными словами (операндами) разной длины. Чаще всего, длина operandov измеряется в *байтах* и кратна степени числа 2. например, процессоры Pentium способны выполнять действия с operandами длиной в 1, 2, 4 или 8 байтов.

Во многих (но не во всех) процессорах разные команды имеют различную длину (но она всегда кратна длине минимальной адресуемой единицы, т.е. длина команды в адресах всегда выражается целым числом). В процессорах x86 длина команды может составлять от 1 до 15 байтов. Команда x86 может начинаться с произвольного адреса.

Бывают процессоры, в которых МАЕ имеют разную длину для команд и для данных. При этом для хранения команд и для хранения данных используются разные (как логически, так и физически, конструктивно) устройства ОЗУ. В таком случае говорят, о двух разных *адресных пространствах* – команд и данных.

Адреса элементов оперативной памяти, подобно командам и данным, во внутреннем представлении в компьютере также представляют собой двоичные слова.

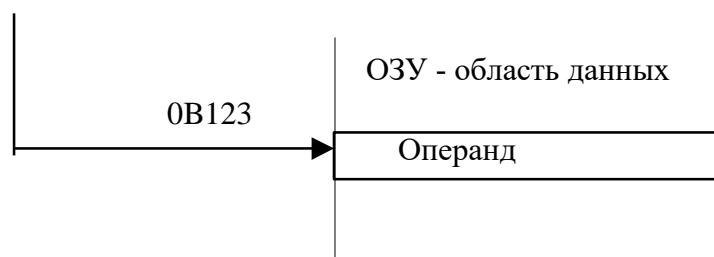

*Примеры команд обращения к памяти:*

`mov ax,[bx];` пересылка одного 16-ти разрядного слова из памяти в регистр `ax`

`add al,[di+2];` суммирование байта из памяти с байтовым регистром и запись в регистр

### **Иерархическая организация памяти**

Подсистема памяти имеет иерархическую, «многослойную» структуру: при переходе по слоям "сверху-вниз" (от процессора) - увеличивается объем и падает скорость.

Рис. 1.9. Иерархическая структура памяти.

Чем определяется соотношение объемов и скоростей «слоев»? Эти характеристики выбираются с целью получить наивысшую производительность при той же цене. Перечислим «слои» памяти ЭВМ:

- 1) **регистры процессора** – это составная часть процессора, которая, однако, выполняет функцию (временного) хранения программных объектов: элементов программного кода, обрабатываемых операндов и их адресов;

- 2) **кэш-память** (может быть, многоуровневая);

- 3) **оперативное запоминающее устройство ОЗУ** (Random Access Memory RAM) – память с произвольной адресацией;

- 4) **внешние ЗУ** (диски) – это память с последовательным доступом;

- 5) **сеть** – с точки зрения хранения данных, сеть ЭВМ, к которой подключен компьютер, может рассматриваться, как огромное, но медленное хранилище информации (Интернет).

С точки зрения понимания того, как проходит процесс выполнения программы, наиболее важное значение имеет часть 3) ОЗУ (основная или оперативная память).

## **1.7. Типовая структура машинной команды в пространстве и во времени. Формат и конвейер команд**

### **Структура машинной команды «в пространстве»**

Структура команды:

|     |                |

|-----|----------------|

| КОП | Адресная часть |

|-----|----------------|

Машинная команда во внутреннем представлении по форме представляет собой *двоичное слово*. Его можно представить состоящим из двух частей (полей): кода операции (КОП) и адресной части команды.

**Код операции** обозначает, что должна сделать команда. Длина битового поля, отведенного в команде под КОП, должна быть достаточной для кодирования всех команд процессора.

Поле КОП может быть переменной или постоянной длины. Некоторые кодовые комбинации поля КОП оставляют незадействованными, это *резервные коды* для будущего расширения системы команд.

**Адресная часть команды** содержит информацию о местоположении одного или нескольких операндов, используемых командой. Операнды или данные в ЭВМ, с которыми машинные команды выполняют действия, по форме также представляют собой двоичные слова. Эти битовые слова часто (но отнюдь не всегда) имеют смысл интерпретировать как числа.

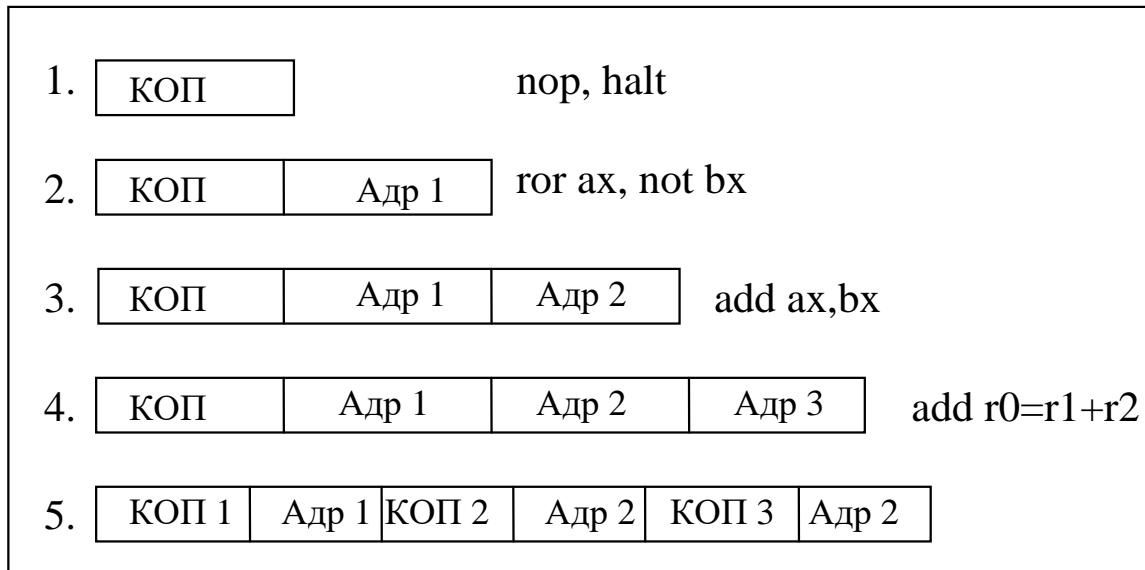

Можно выделить несколько обобщенных форматов команд на основе рассмотрения количества операндов и адресных частей в команде (рис. 1.10).

Рис.1.10. Обобщенные форматы команд.

1. В любой системе команд есть «пустая» команда, которая не делает никакого действия (NOP). Для нее просто не требуется указания operandов. Некоторые команды не требуют указания каких-либо operandов, так как их действие направлено на один заранее предопределенный operand. Например, команда «разрешить прерывание» STI – эта команда устанавливает бит IF в регистре состояний EFLAGS.

2. Некоторые команды выполняют действие с одним operandом. Например, команда NEG – поменять знак operand'a. Такие команды называют одноoperandными. Передача управления – также одноoperandная команда, в которой результат операции – изменение содержимого счетчика команд. В таких командах есть одно адресное поле для указания места расположения (или значения) опаранда.

*Пример* такой команды: изменение знака опаранда:

neg ax ; эта команда изменит знак целого числа в регистре процессора

3. В любом процессоре есть *команды пересылок*, которые копируют содержимое элементов памяти в другие элементы памяти. Такие команды

требуют указания двух операндов: *источника* *Source (Src)* и *приемника Destination (Dest, Dst)*. Пример такой команды:

`mov bl, [esi] ;` Содержимое однобайтового элемента данных из ячейки памяти, адрес которой хранится в регистре процессора *esi* копируется в регистр процессора *bl*.

4. Привычные нам арифметические действия (сложение, вычитание, умножение, ...) оперируют с двумя операндами и формируют результат операции:  $C=A+B$ . Таким образом, в операции участвуют три элемента. В некоторых системах команд (процессоры Power, Alpha) соответствующие команды действительно позволяют программисту независимо указать места расположения всех трех элементов. Для уменьшения длины команды в других системах команд эти команды имеют только два адресных поля, при выполнении команды результат операции помещается на место одного из operandов, замещая («затирая») его.

5. В системах команд процессоров с длинным командным словом (VLIW) одновременно выполняются несколько команд и они должны быть записаны подряд – длинным словом. Формировать длинное слово может или программист (в сигнальных процессорах), или транслятор языка (Itanium).

Из приведенного рассмотрения должно стать понятным, что структура адресной части команды может существенно различаться для разных команд, как по количеству описываемых operandов, так и по способу кодирования информации о том, где расположен operand.

Разработчики системы команд выбирают структуру адресной части команды, исходя из нескольких взаимно-исключающих требований, главные два из которых следующие:

- а) Адресная часть команды должна быть по возможности короткой, чтобы не увеличивалась чрезмерно длина команды.

- б) Должна обеспечиваться достаточная гибкость и универсальность кодирования параметров команды.

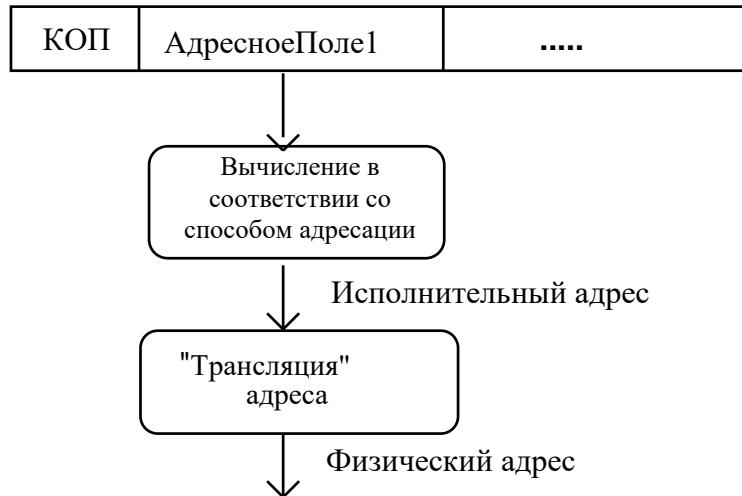

Адрес(а) операнда(ов), с которым(и) выполнит действие команда, определяются в процессе обработки этой команды (формируются *устройством вычисления адресов*). Такой адрес называют *исполнителем* (*executive*) или *эффективным* (*effective*) адресом ЕА. Адрес, который передается по магистрали из процессора в ОЗУ и управляет работой ОЗУ, будем называть *физическим адресом*.

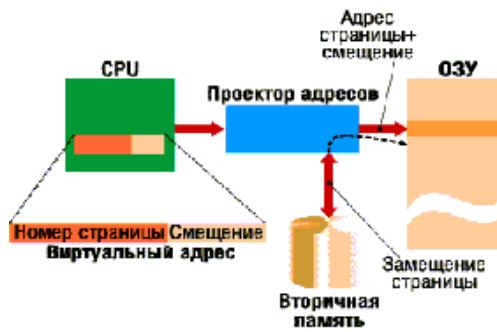

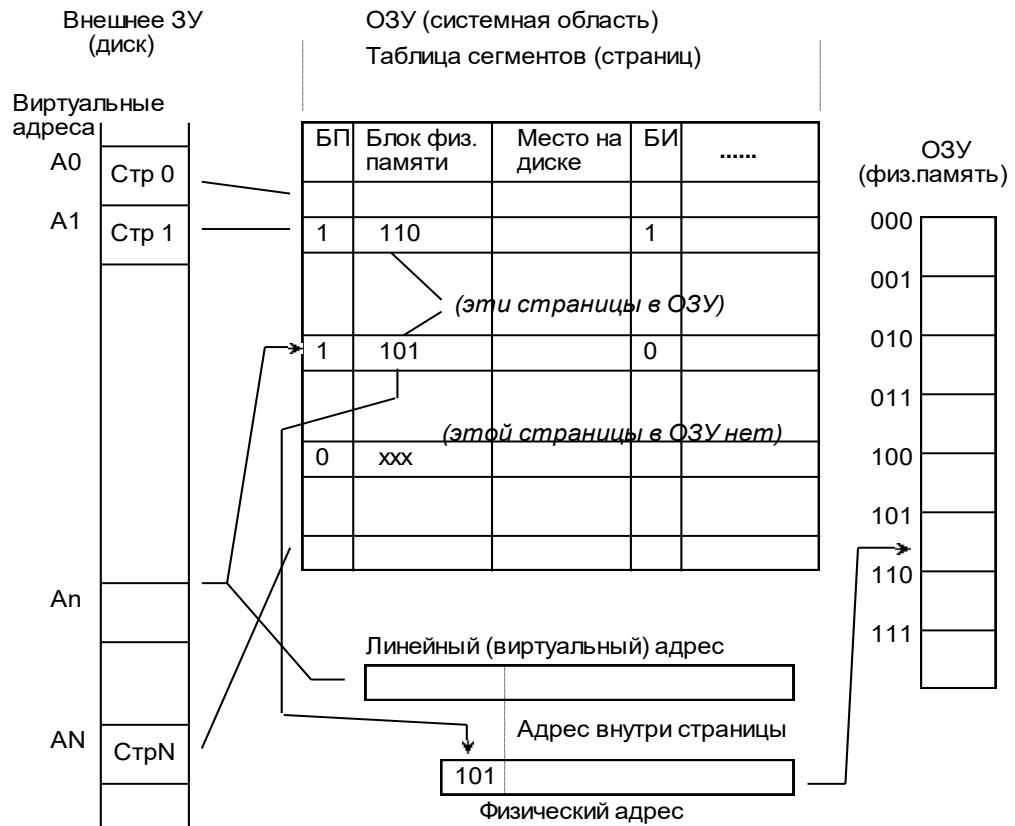

Для того, чтобы получить значение *физического адреса* из значения *исполнительного адреса*, последний в процессоре должен быть подвергнут преобразованию, которое обозначают словосочетанием *трансляция адреса*.

**Понятие адресного пространства является одним из фундаментальных в организации ЭВМ.**

Отдельно следует сказать о *физическом адресном пространстве* – т.е. о пространстве реально формируемых адресов, которым могут соответствовать реально существующие (включенные в систему) элементы памяти. В системах на базе большинства представителей семейства Pentium может быть сформирован физический адрес длиной 32 или 64 бита, т.е. физическое адресное пространство равно  $2^{32}$  или  $2^{64}$ . В любой реальной системе *любое* адресное пространство используется чаще всего не полностью.

Можно сказать, что *трансляция адреса* это операция отображения одного адресного пространства (или может быть его части) на другое адресное пространство (или его часть). В простейших вычислительных системах трансляция адресов может представлять собой просто  *тождественное отображение*, т.е. физический адрес равен исполнительному.

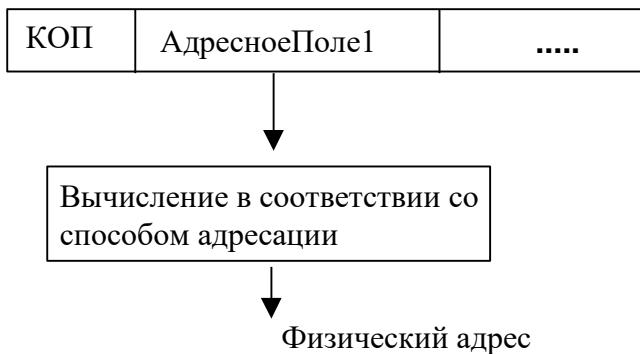

Процедура вычисления физического адреса по содержимому адресной части команды может быть достаточно сложной. Она включает два этапа:

- 1) вычисление *исполнительного/эффективного* адреса ЕА (*executive/effective address*) в соответствии со способом адресации;

- 2) переход от EA к физическому адресу (эта часть вычислений, какуже было сказано, называется "трансляцией адреса").

### Структура команды во времени

Процесс выполнения одной машинной команды может быть разложен на несколько этапов. Разбиение на этапы имеет методическое назначение – оно помогает понять, как взаимодействуют отдельные узлы процессора при выполнении команд. Такое рассмотрение будет сделано непосредственно далее в данном подразделе.

Однако разбиение процесса выполнения команды на отдельные более мелкие этапы при конструировании внутренней структуры и схемотехники процессора позволяет использовать конвейеризацию для увеличения быстродействия процессора структурным путем. Фактически в разных процессорах количество этапов, на которые разбит процесс выполнения команд, может различаться как для разных процессоров, так и для разных команд в одном процессоре.

Процесс выполнения команды может содержать следующие этапы:

|                                      |                    |

|--------------------------------------|--------------------|

| 1.* Выборка команды(fetch F)         | Обращение к памяти |

| 2.* Дешифрация КОП(decode D)         |                    |

| 3. Вычисление адреса операнда        | Обращение к памяти |

| 4. Выборка операнда (read R)         | Обращение к памяти |

| 5.* Исполнение операции(execute E)   |                    |

| 6. Запись результата(retire/write W) | Обращение к памяти |

Опишем более подробно процесс выполнения команд программы.

**Выборка (F1 Fetch).** Процессор байт за байтом считывает из ОЗУ порции программного кода (фрагмент программного кода, соответствующий команде процессора **обязательно** содержит КОП, и, возможно, но необязательно адресную часть) по адресу, который в данный момент содержится в счетчике команд.

После считывания очередной порции программного кода, содержимое счетчика автоматически увеличивается, так, что он всегда содержит адрес байта программы, который должен быть считан следующим.

**Декодирование (D2 Decode).** Процессор декодирует команду - анализирует считанный КОП, и по типу операции, закодированному в КОП, принимает решение о том, какая операция должна быть выполнена (управление АЛУ), а также о том, сколько байтов содержит данная команда и как их следует интерпретировать. Затем следует декодирование адресной части (если она есть). Если декодируемая команда предполагает расположение операнда в памяти, следует этап A3, в противном случае (если операнды расположены только в регистрах процессора) этап A3 отсутствует.

**Вычисление исполнительного адреса (A3 Address Calculation),** в ходе которого процессор формирует физический адрес операнда в памяти. Иногда (но далеко не всегда) для определения составных частей адреса операнда необходимо дополнительное обращение к ОЗУ. По вычисленному адресу происходит затем следующий этап R4:

**Выборка операнда (R4 Read),** для чего (возможно) придется выполнить обращение к ОЗУ. Если адресная часть команды содержит информацию о нескольких операндах, находящихся в памяти, то этапы A3 и R4 будут повторены нужное количество раз. Если операнды располагаются в регистрах процессора, то на этапе R4 обращений к памяти не требуется. За выборкой операндов следует этап E5:

**Исполнение операции (E5 Execute)** - не предполагает обращения к памяти, хотя время выполнения может для разных команд значительно различаться. По окончании этапа исполнения, может быть (но не всегда) придется произвести заключительное действие W6:

**Запись результата (W6 Write)** для чего (возможно) потребуется обращение к ОЗУ.

В зависимости от вида операции, количества операндов, способов адресации структура команды во времени (в частности, требуемое количество обращений к памяти) может сильно различаться для различных команд. Это означает, что для разных команд некоторые этапы могут отсутствовать, и для разных команд длительность во времени (даже одноименных) этапов может быть различной.

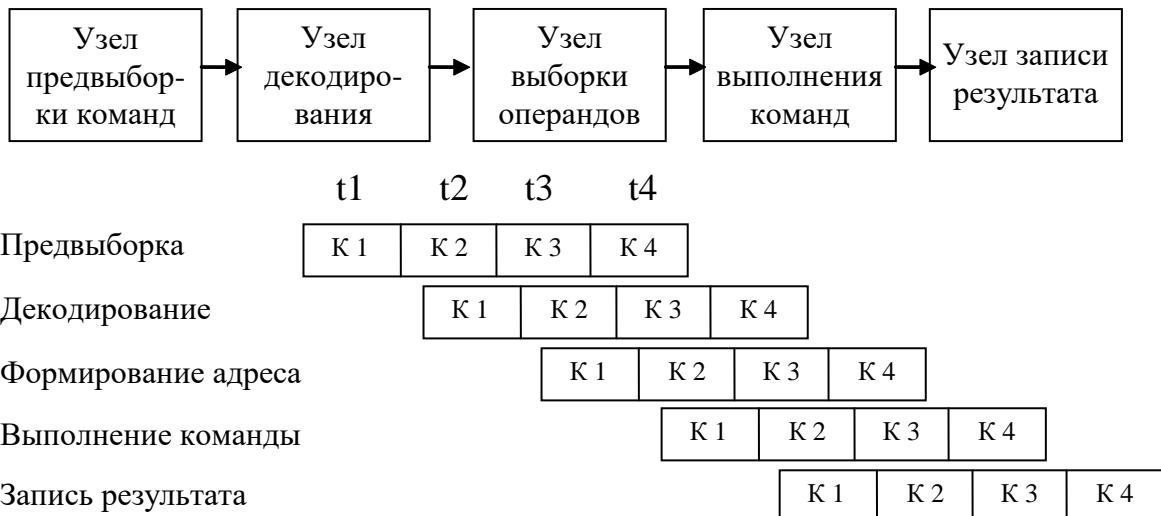

### Конвейеризация

Конвейеризация - параллельное одновременное выполнение разных этапов разных команд. Чтобы такое запараллеливание стало возможным, в процессоре необходимо иметь для выполнения каждого из этапов отдельный исполнительный узел. На рис. 1.11 показаны узлы процессора и конвейер команд. Команды продвигаются из одного узла в другой.

Рис.1.11. Конвейер команд.

Конвейеризация увеличивает пропускную способность процессора (количество команд, завершающихся в единицу времени), но она не сокращает время выполнения отдельной команды. Имеются некоторые накладные расходы на конвейеризацию, возникающие в результате несбалансированности задержки на каждой его ступени. Частота синхронизации (такт синхронизации) не может быть выше, чем время, необходимое для работы наиболее медленной ступени конвейера.

Конвейер не всегда представляет собой линейную цепочку этапов. В ряде ситуаций оказывается выгодным, когда функциональные блоки соединены между собой не последовательно, а в соответствии с логикой обработки. Отдельные блоки в цепочке могут пропускаться, а другие – образовывать циклические процедуры. Это позволяет с помощью одного конвейера вычислять более одной функции.

**Поток команд** - естественная последовательность команд, проходящая по конвейеру процессора. Процессор может поддерживать несколько потоков команд (суперпроцессоры 5 и 6 поколения), если для каждого потока и каждого этапа есть исполнительные элементы.

**Суперконвейер команд** – разбиение каждой ступени на подступени при одновременном увеличении тактовой частоты внутри конвейера; – включение в состав процессора многих конвейеров, работающих с перекрытием. Дробление ступеней позволяет поднять тактовые частоты процессора. К суперконвейерным относятся процессоры, в которых число ступеней больше шести.

| Тип процессора | Количество ступеней конвейера |

|----------------|-------------------------------|

| Pentium III    | 10                            |

| Itanium        | 10                            |

| UltraSPARC III | 14                            |

| Pentium 4      | 20                            |

Суперконвейер ведет не только к увеличению скорости вычислений, но и к возникновению дополнительных сложностей. Возрастает вероятность конфликтов. Дороже встает ошибка предсказания перехода – приходится сбрасывать весь длинный конвейер, на что требуется дополнительное время. Усложняется логика взаимодействия ступеней. Однако за счет использования новых архитектур, удается справиться с большинством проблем. При рассмотрении современных процессоров будут описаны новые идеи:

исполнения команд с изменением последовательности, переименования регистров, спекулятивного исполнения и другие.

### **Основные тенденции в развитии структур средств ВТ**

Основная цель, к которой стремятся, совершенствуя структуру средств ВТ - это повышение производительности на единицу затраченных ресурсов.

Основные пути достижения этой цели связаны с распараллеливанием этапов вычислительного процесса. Современные процессоры и мультипроцессорные системы обеспечивают параллельное выполнение:

1. этапов соседних команд (конвейерная структура процессора)

2. этапов обращения к памяти (конвейерное обращение к памяти)

3. команд (векторный процессор, суперскалярный процессор, VLIW процессор)

4. потоков (нитей) команд (многоядерный и многопотоковый процессор)

5. программ (мультипроцессорная система, сеть)

## ГЛАВА 2. ВИДЫ ДАННЫХ, ИХ КОДИРОВАНИЕ, КОМАНДЫ

Если вы прочитаете содержимое любой ячейки памяти, то вы увидите набор битов. Вы не скажете что это – команда, число, символ или др. На физическом уровне все виды данных и команды в ЭВМ представляются одинаково в виде битов (символов 0 и 1), которым соответствует два уровня напряжения 0В и 5В. Рассмотрим, как и какие данные могут быть закодированы (двоичным кодом), какие команды предназначены для работы с ними.

| №  | Вид         | Команды                                   | Форма представления    | Параметры                         |

|----|-------------|-------------------------------------------|------------------------|-----------------------------------|

| 1. | Числа       | Арифметические: + - * / > <               | Код числа              | Диапазон и точность представления |

| 2. | Тексты      | Строковые и сравнения (совпадает или нет) | Строка символов        | Алфавит                           |

| 3. | Изображения | Обраб. фрагмента (перенос, заливка и др.) | Пиксел (полутон, цвет) | Формат                            |

**Числа.** Этот вид данных был первым, с которым работали средства ВТ. Числа делятся на числа без знака, со знаком и с плавающей запятой. Основными операциями над числами являются арифметические операции.

**Тексты.** Как только было осознано, что компьютер может не только "вычислять", а является универсальным обработчиком данных, стали использовать ВТ для обработки текстов.. Основной объем данных у человечества накоплен был в символьной (текстовой) форме. До средств ВТ уже были разработаны способы кодирования текстов для передачи (телеграф). Основные операции, которые надо было выполнять с текстами – это:

- поиск в тексте фрагментов с заданным содержимым (вхождения подстроки в строку),

- сортировка (последовательности строк), по заданному критерию (например, по алфавиту),

- конкатенация (соединение) строк.

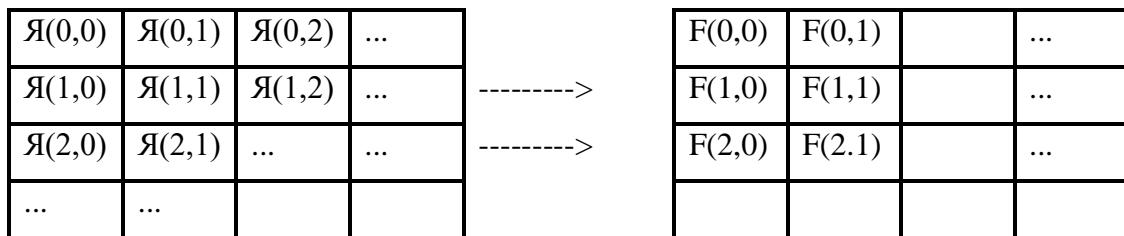

**Изображения** - человек получает через зрительный канал около 90% информации. До недавнего времени основной проблемой для обработки изображений был большой потребный объем ресурсов ( $1000 \times 1000$  пикселов - типовой размер). Операции над изображениями: фильтрация, заливка фрагмента, оконтурирование, перенос фрагмента и др.

**Битовые поля** - вид данных, когда отдельные элементы данных имеют разный размер (в битах), (нередко меньший, чем МАЕ) и напрямую не адресуются процессором. Характерный пример - отдельные поля в машинной команде (этот вид данных является выходным для трансляторов). Другой пример - входные данные, получаемые управляющими ЭВМ (микроконтроллерами) с объекта управления. Обращение к битовым полям требует дополнительных команд процессора для маскирования и сдвига. Операции над многобитовыми полями: извлечение битового поля, сборка одного числа из битовых полей, замена битового поля, проверка отдельного бита, переключение битов и др.

Например, для переключения битов (с 0 на 1, с 1 на 0) надо сложить х командой «Исключающее ИЛИ» с маской, у которой в соответствующих позициях единицы.

**Прочие виды** - .... (например, данные, описывающие звуки) и многое другое, с чем пока еще работают не очень много.

Видим, что перечисленные виды отличаются не только по содержанию, форме представления, параметрам, но и командам, которые необходимо выполнить при их обработке.

## **2.1. Числа и системы счисления**

Характеристики чисел – диапазон представимых значений и точность представления.

Цифровое представление величин, когда определено выбран формат представления (т.е. например выбрана разрядность, система счисления,.), имеет два присущих свойства :

- а) ограничен диапазон представимых значений (их при  $N$ -битовом коде не более, чем  $2^N$  штук);

- б) ограничена точность (разрешающая способность) представления величины - нельзя отобразить изменение, меньшее некоторого кванта (единицы младшего разряда при целочисленном представлении);

- в) представление чисел оказывается «циклическим» по отношению к арифметическим действиям.

Форма представления данных во всех современных средствах ВТ - двоичный код. Это означает, что число изображается двоичным кодом. (Вначале пытались строить вычислительные устройства, работающие в десятичной системе счисления, поскольку десятичная система счисления привычна для человека. Но потом стало ясно, что технически проще реализовать элементы с малым количеством дискретных устойчивых состояний. Некоторые старые виды логических элементов использовали троичную систему счисления, но сегодня все работают в двоичной)

### **Системы счисления**

**Система счисления** - совокупность правил представления и записи чисел.

**Алфавит системы счисления** - набор символов. Отдельные символы - буквы алфавита или цифры.

**Основание СС** - число символов в алфавите.

**Слово** или просто число - комбинация символов, изображающая число.

## **Виды систем счисления.**

**1. Непозиционные** - значимость каждого символа в словах определяется только его начертанием и независит от его положения (позиции) в слове. Пример: Римская - Алфавит: I V X L C D M; Число LXXVII= L+X+X+V+I+I

**2. Позиционные** - значимость каждого символа определяется как символом, так и его местом (позицией). **Основание** - количество цифр в алфавите. Если основание N, то N-ричная сист. счисления. **Разрядная сетка** - совокупность возможных положений символов в словах. В разр.сетке веделяют место разделения слов на целую и дробную части, в этом месте ставится “запятая”. Разряды располагаются и нумеруются вправо и влево от запятой. Каждому разряду придается “вес”  $P_k$ . **Весовая функция** - распределение весовых коэффициентов по разрядной сетке  $P_k=f(k)$ .

**3. Однородная позиционная** -  $P_k=n^k$ . Пример: восьмеричная, десятичная.

### **Восьмеричное изображение**

$$A = a_{n-1}10^{n-1} + a_{n-2}10^{n-2} + \dots + a_010^0 + \dots + a_{-m}10^{-m} = a_{n-1}8^{n-1} + a_{n-2}8^{n-2} + \dots + a_08^0 + a_{-1}8^{-1} + \dots + a_{-m}8^{-m}$$

### **Десятичное изображение**

$$N = 12345 = 1*10^4 + 2*10^3 + \dots + 5*10^0$$

### **Двоичное изображение**

$$N = 10011_b = (1*10^{100} + 0*10^{11} + 0*10^{10} + 1*10^1 + 1*10^0)_{bin} = (1*2^4 + 0*2^3 + 0*2^2 + 1*2^1 + 1*2^0)_{dec}$$

### **Шестнадцатиричное**

$$N = B4F1h = B*10^3 + 4*10^2 + F*10^1 + 1*10^0 = 11*16^3 + 4*16^2 + 15*16^1 + 1*16^0$$

**4. Неоднородная позиционная** - весовая функция не представляет простую показательную функцию. Пример: время, двоично-десятичная.

**5. С непосредственным изображением чисел** - один знак - один символ.

**6. С кодированным изображением чисел** - число кодируется несколькими символами. **Пример: бинарно-кодированные системы** - каждая цифра исходного числа кодируется с использованием алфавита двоичной системы. Для кодирования десятичных чисел используются четыре двоичных разряда и веса разрядов могут быть: 8-4-2-1, 7-4-2-1, 5-4-2-1 и др.

Одноразрядное число:  $Y = \sum z_i p_i$ ;  $z_i$  - двоичная цифра,  $p_i$  - коэф-т веса.

Преобразование представления чисел из одной системы в другую

ЭВМ имеет устройства (регистры и АЛУ) с ограниченной разрядностью, поэтому числовая система ЭВМ конечна (может представить ограниченное количество чисел) и циклична, что наблюдается при последовательном прибавлении 1. Пример цикличности:  $11111111 + 1 = 00000000$  (теряется бит переноса).

Два способа:

**Начиная с младших разрядов** – последовательным делением на основание той системы счисления, в которую хотим преобразовать. Остатки от деления дают последовательно цифры кода, начиная с младшей.

|    |   |

|----|---|

| 13 | 2 |

| 6  | 1 |

| 3  | 0 |

| 1  | 1 |

| 0  | 1 |

Пример: - Из десятичной в двоичную - деление на 2 , запись остатка.

- Обратный перевод - сложение двоичных чисел с учетом их веса.

$$1*2^3 + 1*2^2 + 0*2^1 + 1*2^0 = 8+4+0+1=13$$

**Начиная со старших разрядов** – последовательным вычитанием степеней основания той системы счисления, в которую хотим преобразовать. Знак результата дает последовательно цифры кода, начиная со старшей.

## 2.2. Представление и команды над целыми числами

### Целые числа без знака

Целые числа используются для обозначения того, что можно считать "на штуки". Подсчитываемые "штуки" могут относиться как к вещественным объектам

(данные вводятся извне), так и к внутренним, например количество циклов в программе. В частности это могут быть адреса элементов данных в памяти.

Представление чисел оказывается циклически повторяющимся. Цикличность представления и ограниченность диапазона приводят к тому, что итогом операции может быть либо **правильный результат, либо выход за границу** диапазона (этот выход называют термином "переполнение" (разрядной сетки)).

Диапазон представимых значений в  $N$ -битовой сетке можно записать таблицей в разных системах счисления: При возникновении переполнения его хотелось бы в процессоре обнаружить, а также определить, в какую сторону оно произошло: получился ли результат "больше максимального представимого числа" (при сложении) или "меньше минимального" (при вычитании).

Табл. 2.1. Диапазон представимых значений в  $N$ -битовой сетке

| HEX     | BIN       | DEC       | К след. зн. |

|---------|-----------|-----------|-------------|

| 00...00 | 000...000 | 0         | +1          |

| 00...01 | 000...001 | 1         | +1          |

| 00...02 | 000...010 | 2         | +1          |

| .....   | .....     | .....     | ...         |

| ...FFD  | 111...101 | $2^{N-3}$ | +1          |

| ...FFE  | 111...110 | $2^{N-2}$ | +1          |

| ...FFF  | 111...111 | $2^{N-1}$ | +1          |

| 00...00 | 000...000 |           | +1          |

| 00...01 | 000...001 |           |             |

Здесь проходит граница цикла

При обнаружении переполнения (а также и других «экстраординарных», нештатных ситуаций) возможны различные способы реакции:

- a) проигнорировать

- б) остановить выполнение программы

- в) предпринять заранее предусмотренные действия.

**Замечание о разрядности:** во многих процессорах возможно выполнение операций с операндами разной разрядности (обычно от минимально адресуемой единицы (МАЕ) до Слова).

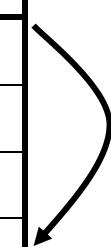

Рис. 2.1. Круговая диаграмма представления чисел.

Очень наглядно изображать циклическость представления целых чисел в ограниченной разрядной сетке с помощью круговой диаграммы, изображенной слева. Эта диаграмма хорошо иллюстрирует переход к следующему числу путем прибавления 1, переход к предыдущему путем вычитания 1, сложение чисел как сложение эквивалентных углов, а также явления переполнения для беззнаковых чисел и чисел со знаком.

### Переполнение и расширение разрядности

В большинстве процессоров в случае переполнения разрядной сетки устанавливается специальный флаг переполнения - С-бит.

|                                                                      |                                    |

|----------------------------------------------------------------------|------------------------------------|

| $+ \quad a_{n-1} a_{n-2} \dots a_1 a_0$                              | первый operand                     |

| $\underline{b_{n-1} b_{n-2} \dots b_1 b_0}$                          | второй operand                     |

| $C \leftarrow s_{n-1} s_{n-2} \dots s_1 s_0$<br>устанавливает С-бит) | сумма (если возникает перенос – он |

$a_{n-1} a_{n-2} \dots a_1 a_0$       первый операнд

$b_{n-1} b_{n-2} \dots b_1 b_0$       второй операнд

$C \leftarrow s_{n-1} s_{n-2} \dots s_1 s_0$       разность (если возникает заем – он

устанавливает С-бит)

Пример переполнения чисел в 8-разрядном регистре.

$$254+7=5$$

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

Если диапазон представимых чисел в данной разрядной сетке мал, можно использовать представление чисел с повышенной разрядностью – перейти от *char* к *int* или к *double*. И далее использовать для представления операнда два или три или более слов.

В некоторых процессорах (команды *MMX-SSE*) может использоваться так называемая «арифметика с насыщением» (*saturation*) при выходе результата за границу представимого диапазона процессор подставляет в качестве результата ближайшее к нему представимое число. Приведем пример насыщения чисел на границах диапазона.

$254+7=255$

$1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1$

$1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1$  Насыщение на

верхней границе

$7-254=0$

$0 \ 0 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1$

$1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 0$

$0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0$  Насыщение на

нижней границе

## Целые со знаком: дополнительный код

Для кодирования знака используют следующие коды:

**Прямой код.** Знаковый разряд - единица, цифровые разряды без изменения.

**Дополнительный код.** Знаковый разряд - единица, цифровые разряды инвертируются и к младшему разряду добавляется единица. Доп.код позволяет производить замену операции вычитания сложением дополнительных кодов. Правило  $[X]_{\text{доп}} + [Y]_{\text{доп}} = [X+Y]_{\text{доп}}$  выполняется всегда.

Декодирование такое же, как и кодирования. Используется в ЭВМ.

**Обратный код.** Знаковый разряд - единица, цифровые разряды инвертируются. При сложении чисел единица переноса добавляется в младший разряд.

**Модифицированные коды.** Под знак отводят два разряда: старший - знаковый, младший - переполнения.

| Число   | Прямой код | Дополнительный код | Обратный код | Модифицированный код, обратный |

|---------|------------|--------------------|--------------|--------------------------------|

| -0,1101 | 1,1101     | 1,0011             | 1,0010       | 11,0010                        |

Дополнительный код (английский эквивалент: two's complement) получается естественным образом - последовательным вычитанием 1 из нуля. Представление чисел со знаком в дополнительном коде также будет циклическим.

Дополнительный код хорош тем, что в нем действия сложения и вычитания над беззнаковыми числами и над числами со знаком выглядят одинаково. Это эквивалентно утверждению, что «дополнительный код суммы чисел равен сумме дополнительных кодов слагаемых».

Табл. 2.2. Диапазон представимых значений в  $N$ -битовой сетке.

| HEX     | BIN       | DEC      | К предыд.<br>зн. |

|---------|-----------|----------|------------------|

| 10...00 | 100...000 | $-2^N-1$ | -1               |

| .....   | .....     | .....    |                  |

Наименьшее

отрицательное число

|         |           |             |    |

|---------|-----------|-------------|----|

| 1..FFE  |           | -2          | -1 |

| 1..FFF  | 111...111 | -1          | -1 |

| 00...00 | 000...000 | 0           | -1 |

| 00...01 | 000...001 | 1           | -1 |

| 00...02 | 000...010 | 2           | -1 |

| .....   | .....     |             |    |

| 0..FFF  | 011...111 | $2^{N-1}-1$ | -1 |

Наибольшее

положительное число

Обратите внимание на то, что в выбранной разрядной сетке используются для представления чисел все кодовые комбинации, т.е. любой последовательности единиц и нулей в коде соответствует какое-то числовое значение. (При представлении чисел в форматах плавающей точки это будет не так !)

Граница на числовом круге выбирается так, чтобы диапазон был симметричен относительно нуля. Однако полной симметрии не получается. Наименьшее отрицательное число не имеет положительного эквивалента. Кроме того, при такой границе, **старший бит кода играет роль знакового**: 0 соответствует положительным числам, а 1 - отрицательным.

В дальнейшем, говоря о представлении отрицательных чисел, будем иметь в виду использование дополнительного кода, если специально не оговорено иное.

Действия над целыми числами и машинные команды

Какие операции надо производить с целыми числами? Интуитивно это в первом приближении понятно: Арифметические действия: + - \* / . Сравнение целых чисел: > < =

Каков минимальный набор команд? Оказывается, он очень невелик. (Более сложные команды можно реализовать как комбинации простых). Некоторые такие комбинации со временем реализуют в уровне машинных команд.

|           |                                          |

|-----------|------------------------------------------|

| Деление   | последовательность вычитаний и сравнений |

| Умножение | последовательность сложений и сдвигов    |

| Вычитание | сложение с отрицательным операндом       |

|                                      |                                                                |

|--------------------------------------|----------------------------------------------------------------|

| <b>Смена знака</b>                   | инвертирование и прибавление 1                                 |

| <b>Сложение</b>                      |                                                                |

| <b>Сдвиг</b>                         | (что делать с битами, выходящими за пределы разрядной сетки ?) |

| <b>Увеличение (/уменьшение) на 1</b> | по честному со всеми переносами и, возможно, с переполнением   |

В этой таблице некоторые вышестоящие операции могут быть выполнены как комбинации некоторых нижестоящих.

Приведем пример сложения двух чисел разных знаков.

$$\begin{array}{ccccccc} -2+7=5 \\ \begin{array}{ccccccc} 0 & 0 & 0 & 0 & 1 & 0 & 2 \\ 1 & 1 & 1 & 1 & 0 & 1 & \text{инверт} \\ 1 & 1 & 1 & 1 & 1 & 0 & +1->-2 \\ 0 & 0 & 0 & 1 & 1 & 1 & 7 \\ 0 & 0 & 0 & 1 & 0 & 1 & 5 \end{array} \end{array}$$

Приведем пример сложения двух отрицательных чисел.

$$\begin{array}{ccccccc} -2-7=-9 \\ \begin{array}{ccccccc} 0 & 0 & 0 & 0 & 0 & 0 & 1 & 0 & 2 \\ 1 & 1 & 1 & 1 & 1 & 1 & 0 & 1 & \text{инверт} \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 0 & +1->-2 \\ 1 & 1 & 1 & 1 & 1 & 0 & 0 & 1 & -7 \\ 1 & 1 & 1 & 1 & 0 & 1 & 1 & 1 & -9 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 & \text{инверт} \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 1 & +1->-9 \end{array} \end{array}$$

#### Переполнение при действиях над числами со знаком.

При сложении беззнаковых чисел - переполнение происходит, если при действии пересекается граница разрыва  $11\dots11 <-> 00\dots00$ .

При сложении чисел со знаком: если знаки разные - переполнения быть не может.

Если знаки одинаковые, и знак результата - совпадает со знаками операндов - переполнения нет; противоположен знаку операндов - переполнение есть. При действиях над числами со знаком переполнение происходит, если пересекаем границу разрыва  $011..11 - 10..00$ . Для

регистрации этих фактов в процессоре обычно делают два триггера (чаще всего они входят в состав регистра состояний). Содержимое этих триггеров называют битами признаков или флагами.

**C (или cf -от CARRY - перенос)** регистрирует при выполнении многих операций перенос/заем из старшего (знакового) разряда за границу разрядной сетки

**V (или of от OVerFlow - переполнение)** - регистрирует перенос/заем в старший (знаковый) разряд.

Если диапазона представимых значений не хватает, можно искусственно увеличить разрядность - хранить величины в нескольких машинных словах - тогда действия над ними, даже такие простые, как сложение и вычитание потребуют большего количества действий.

### **Команды для действий с целыми числами**

Далее описывается действие основных команд, имеющихся в большинстве процессоров, примеры мемоник приводятся для системы команд *iXX86*.

#### **Сложение и вычитание**

Обе операции трехоперандные: два слагаемых и результат. Формат команды может быть:

3-х operandным –

2-х operandным – результат помещается на место одного из слагаемых (так в *iXX86*)

1-operandным – второй operand и сумма находятся в предопределенном месте (в регистре-аккумуляторе)

нуль-operandным – оба операнда находятся в предопределенных местах (чаще всего это стек).

**add a, b    a ← a + b** так принято в Intel – ассемблере, т.е. результат сложения помещается на место операнда **a**. Аналогично для вычитания : **sub a, b**

**Приятная особенность дополнительного кода** для представления отрицательных чисел:

*Результат действий сложения и вычитания при использовании дополнительного кода имеет один и тот же вид, независимо от того, интерпретируются ли операнды как беззнаковые или как знаковые. Для действий умножения и деления это не так.*

Глядя на двоичное представление целого числа, невозможно сказать, знаковое оно или беззнаковое.

При выполнении операции схемотехника процессора изменяет значения битов **cf** и **of**. Анализируя эти биты, можно узнать, не выходит ли результат сложения или вычитания за пределы представимого диапазона. (Как это сделать, узнаем позже).

Если не хватает разрядности, поддерживаемой АЛУ, то можно искусственно увеличить разрядность - хранить величины в нескольких машинных словах. Рассмотрим, как можно организовать сложение двух «длинных» операндов, используя «короткое» сложение.

$$\begin{array}{r} + a_{n-1} \ a_{n-2} \dots \ a_1 \ a_0 \\ + \mathbf{cf} \leftarrow b_{n-1} \ b_{n-2} \dots \ b_1 \ b_0 \\ \hline + a_{2n-1} \ a_{2n-2} \dots \ a_{n-1} \ a_n \\ + b_{2n-1} \ b_{2n-2} \dots \ b_{n-1} \ b_n \\ \hline \mathbf{cf} \leftarrow b_{2n-1} \ b_{2n-2} \dots \ b_{n-1} \ b_n \quad b_{n-1} \ b_{n-2} \dots \ b_1 \ b_0 \end{array}$$

Результат переноса при сложении младших частей регистрируется в флаге **cf**. Его значение надо учитывать при сложении старших частей.

Для учета при сложении значения флага переноса **cf** в систему команд добавляют **команду сложения с переносом**: **adc a, b** (работает так: **a ← a + b + cf**)

Последовательность команд при выполнении сложения с двойной точностью может быть такой

|                          |                                                      |

|--------------------------|------------------------------------------------------|

| add b0, a0<br>adc b1, a1 | ; b0 ← b0 + a0 (перенос в cf)<br>; b1 ← b1 + a1 + cf |

|--------------------------|------------------------------------------------------|

В некоторых системах команд (например DEC16) команда **adc** однооперандная : **a=a+cf** и тогда так:

|                   |                                             |

|-------------------|---------------------------------------------|

| <b>add b0, a0</b> | <b>; b0 <math>\leftarrow</math> b0 + a0</b> |

| <b>adc b1</b>     | <b>; b1 <math>\leftarrow</math> b1 + cf</b> |

| <b>add b1, a1</b> | <b>; b1 <math>\leftarrow</math> b1 + a1</b> |

// Вопрос о тройной

точности

**Как перейти от представления с одинарной точностью к представлению с двойной ?** Для положительных чисел просто - старшее слово - нулевое.

Для отрицательных - **операция расширения знака** (Sign Extension). Ее действие состоит в заполнении старшего слова знаковыми битами младшего. В системе команд *iXX86* есть команды **cbw** преобразования 8 бит  $\rightarrow$  16 бит, **cwd** преобразования 16 бит  $\rightarrow$  32 бит и **cdq**.

#### Умножение и деление

При умножении  $n$ -разрядных операндов, результат может иметь разрядность до  $2n$ . Поэтому переполнение разрядной сетки при умножении будет возникать гораздо чаще, чем при сложении (т.е. при большей доле комбинаций сомножителей). В системах команд не очень примитивных процессорах есть команды умножения и деления, однако для знаковых и для беззнаковых операндов команды должны быть разные.

В большинстве процессоров АЛУ устроено так, что соотношение разрядностей операндов и результата в командах умножения и деления следующее:

$$(n) * (n) = (2n), \quad (2n) / (n) = (n)_q(n)_r, \text{ т.е. разрядность произведения и делимого вдвое больше. Что делать с «длинным» результатом – проблема программиста.}$$

Как ведут себя флаги при выполнении команд умножения и деления, следует смотреть в полном описании команд.

Частный случай умножения – умножение на степень 2-х, (т.е. на степень основания системы счисления) можно реализовать сдвигом операнда на

соответствующее число разрядов влево для положительной степени или вправо для отрицательной. Для этого в системе команд может иметься **команда арифметического сдвига**. При арифметическом сдвиге вправо (деление на степень двойки) знаковый разряд числа сохраняет свое значение неизменным, а при сдвиге влево (умножение на степень двойки) правый конец операнда заполняется нулями. Если при сдвиге влево знаковый разряд операнда изменил свое значение – это означает, что при умножении произошло переполнение (выход за пределы диапазона представимых значений), это вызывает изменение флагов **cf** и **of**

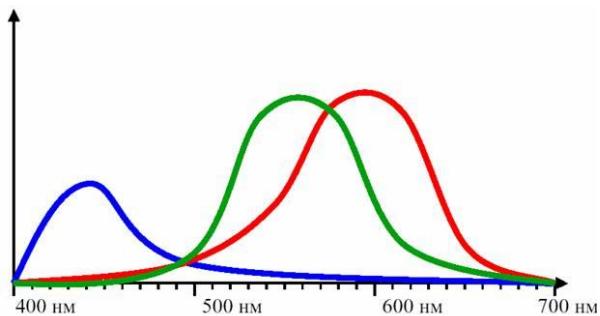

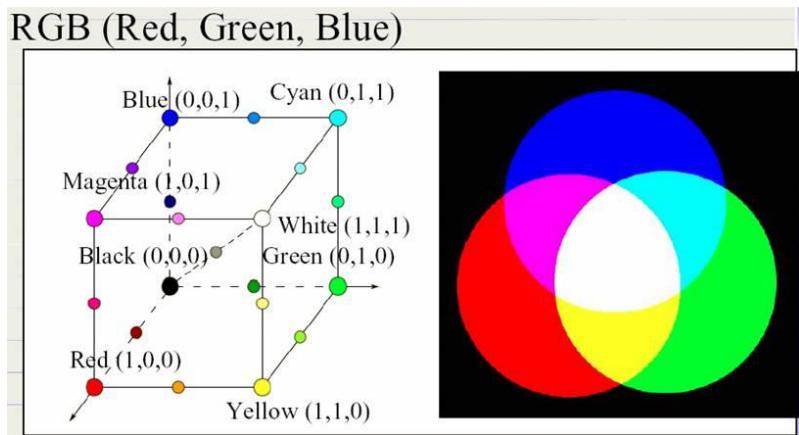

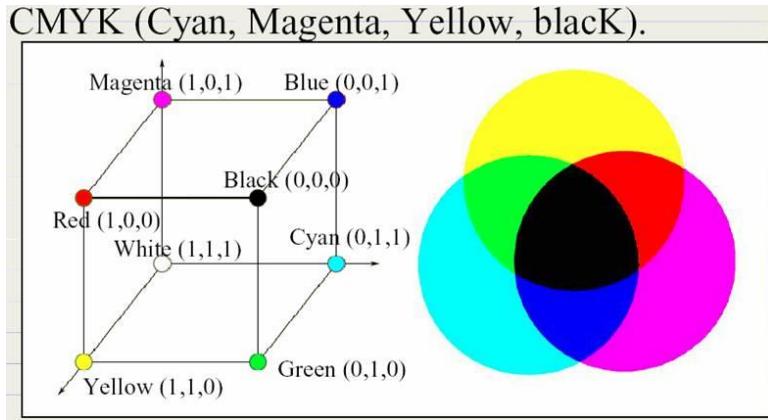

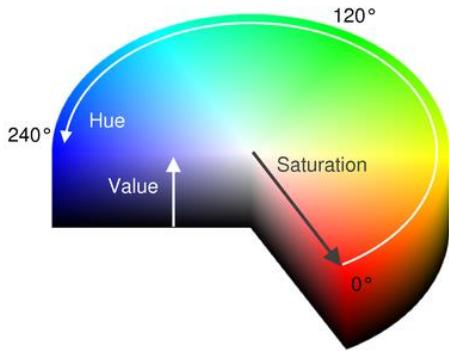

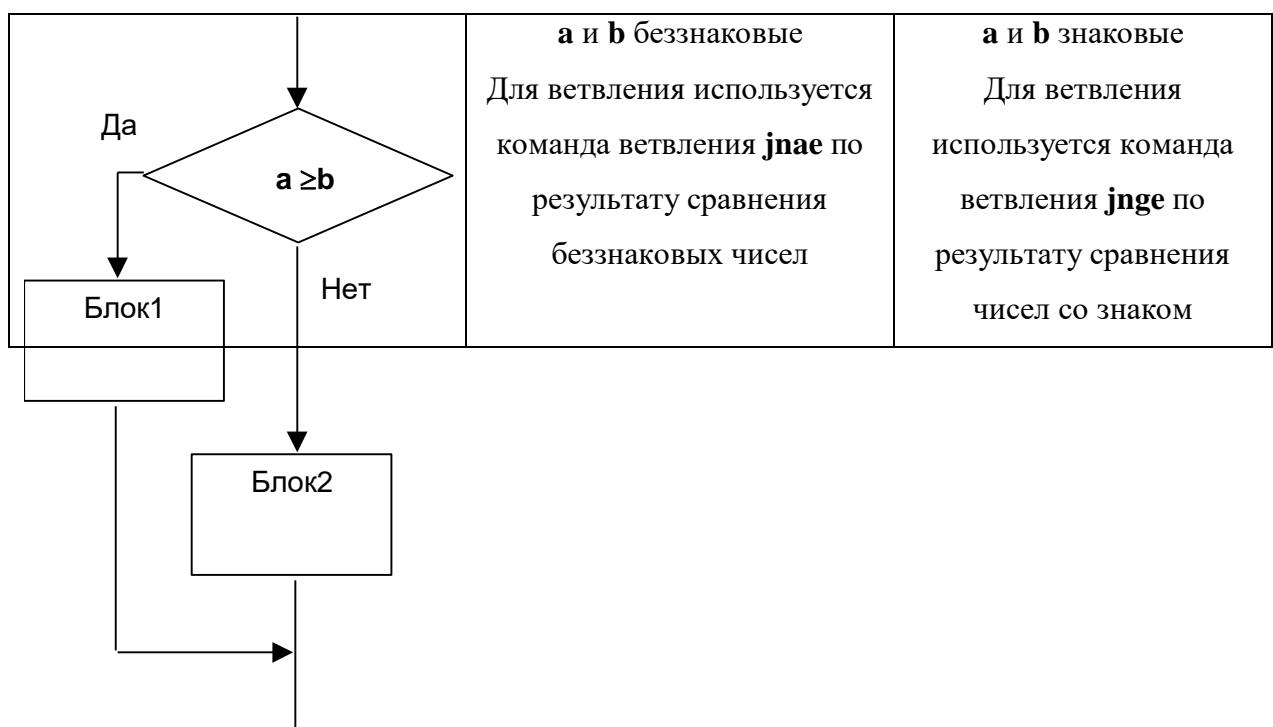

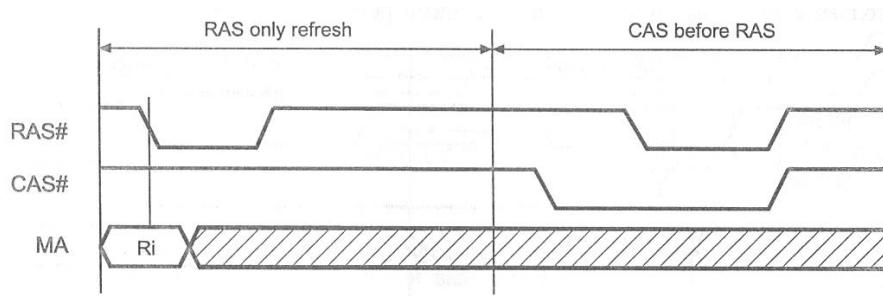

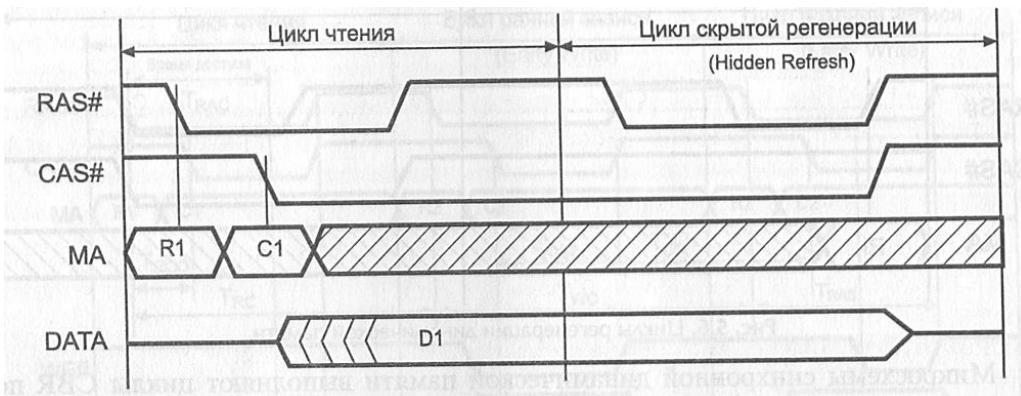

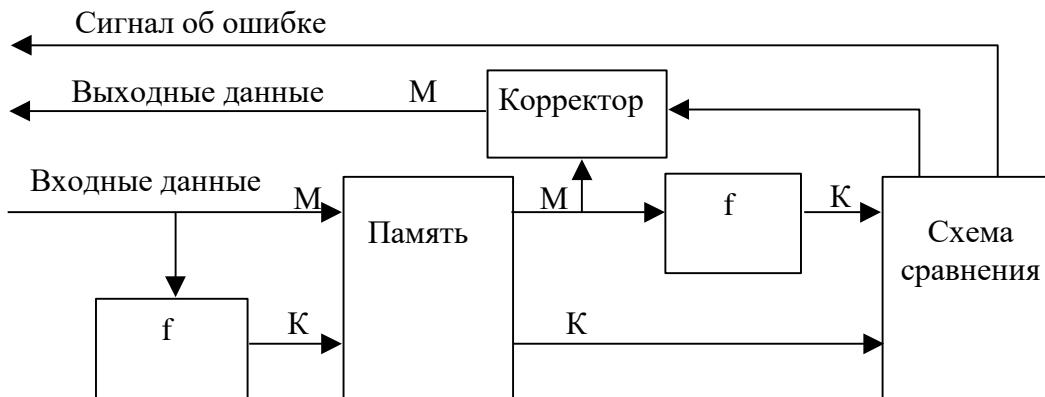

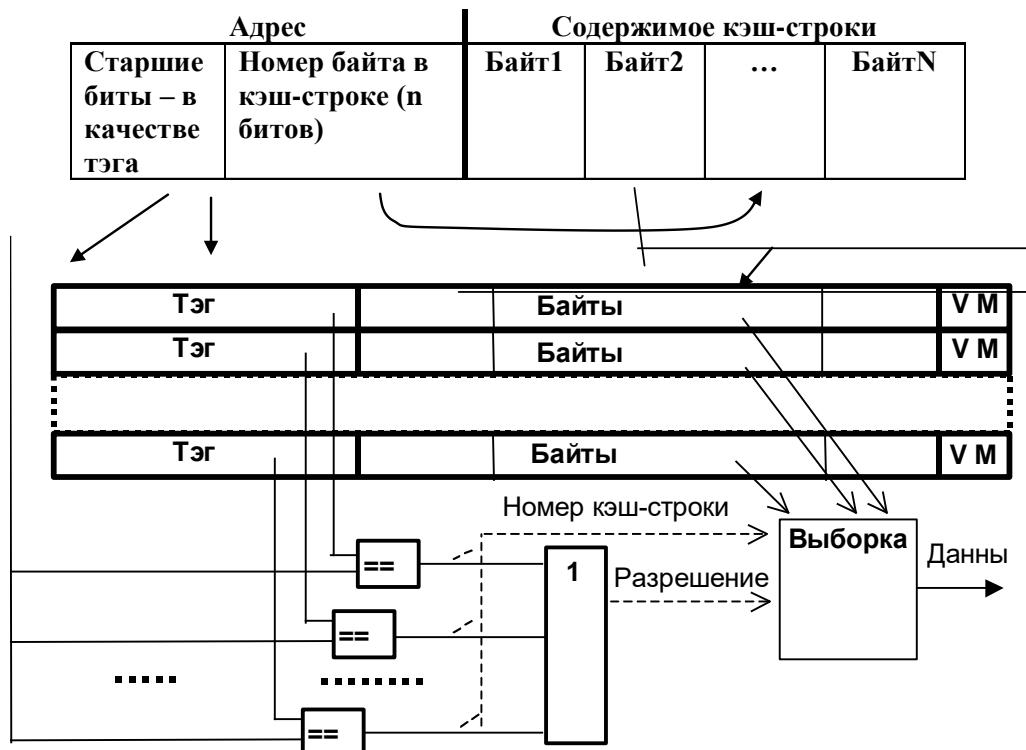

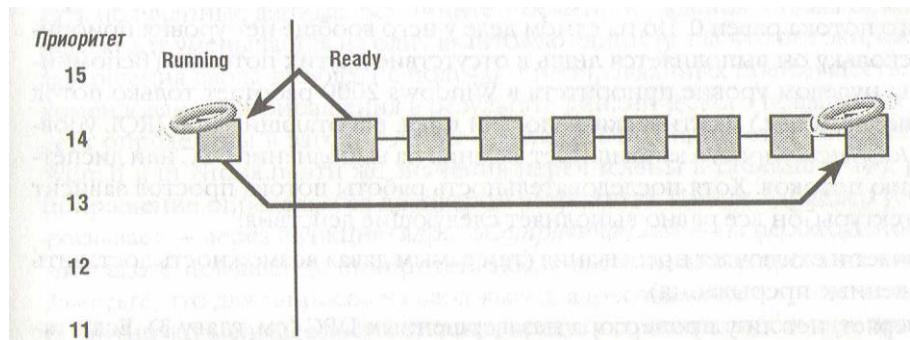

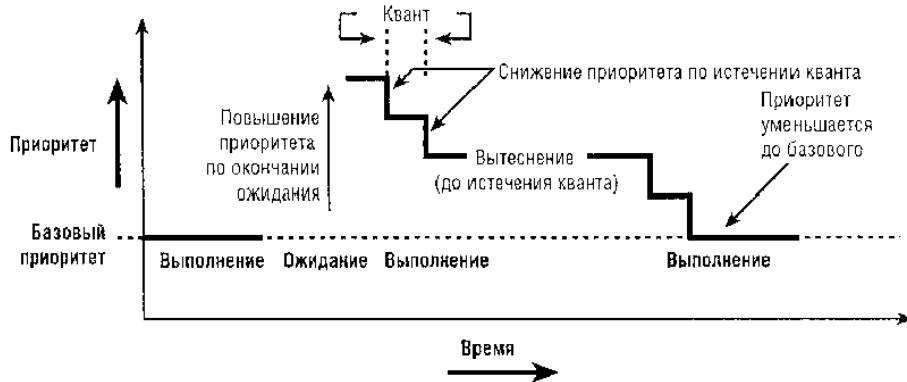

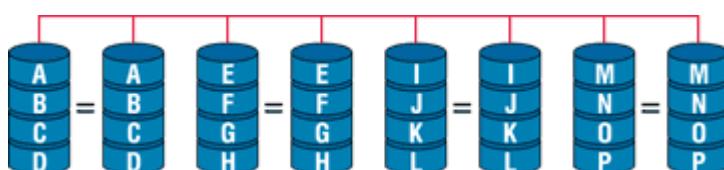

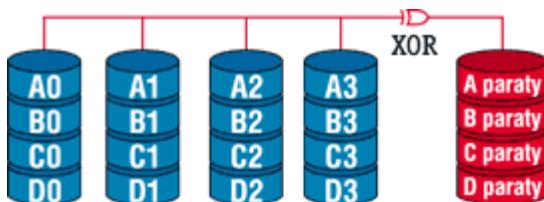

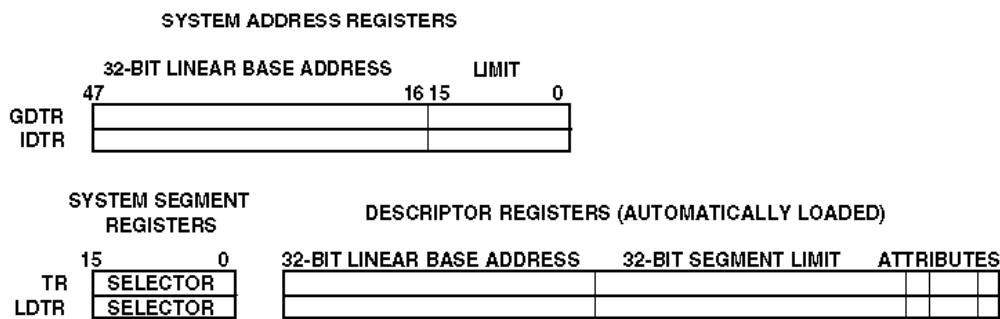

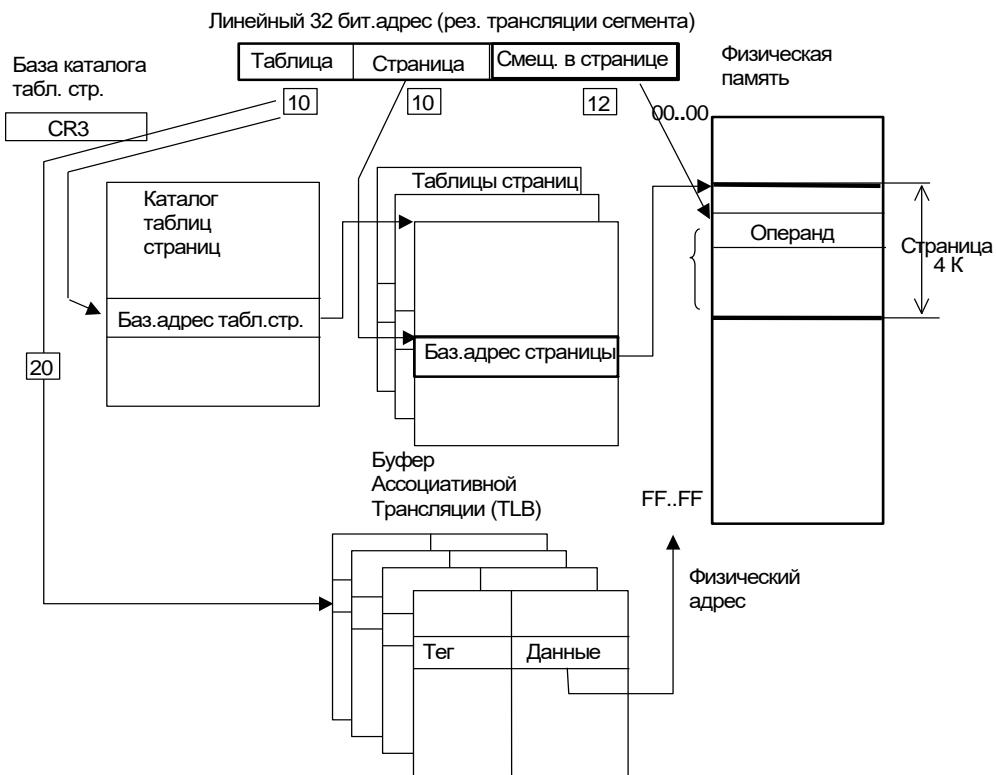

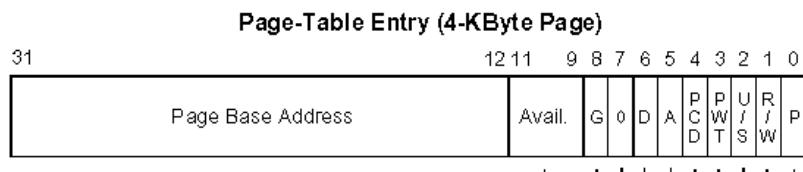

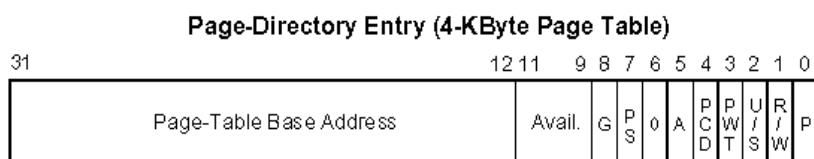

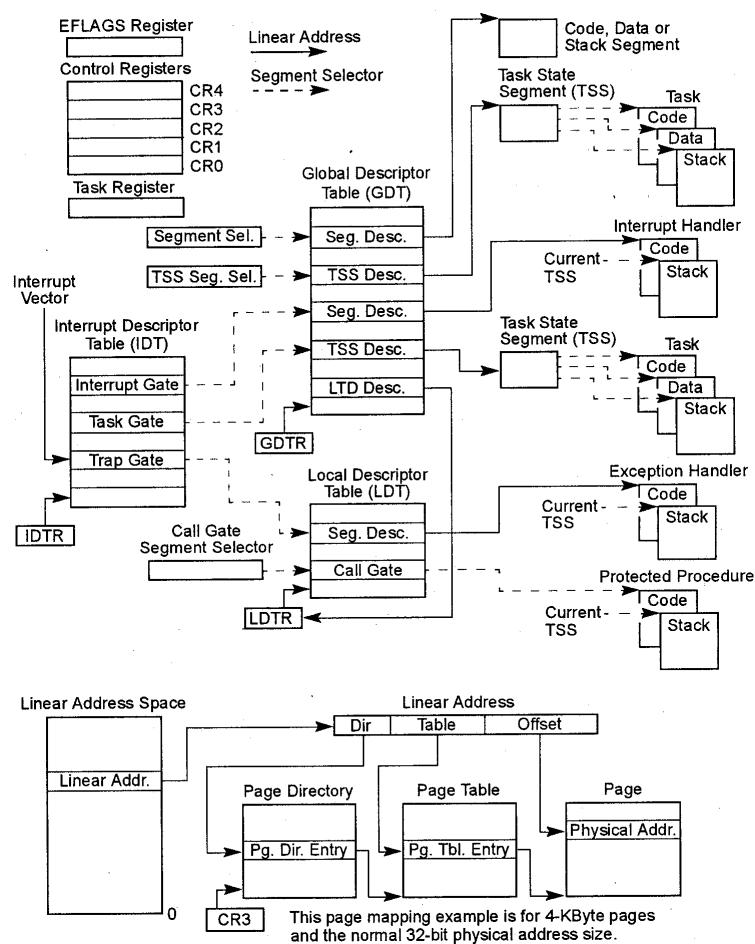

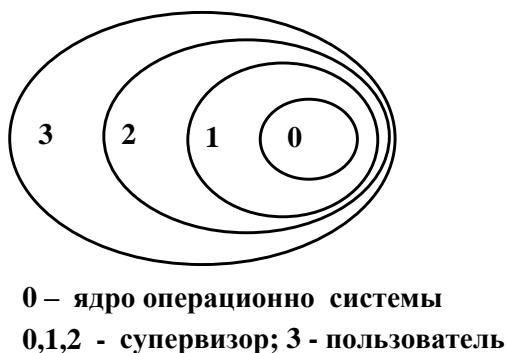

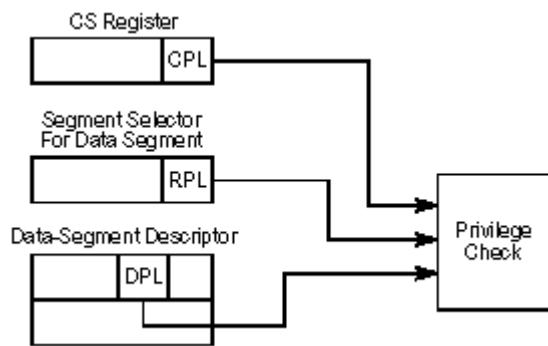

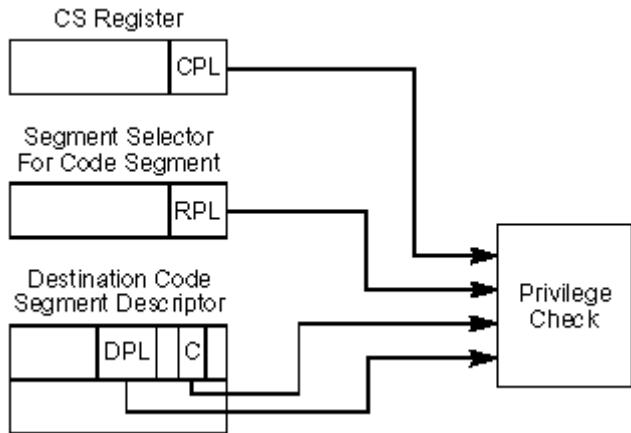

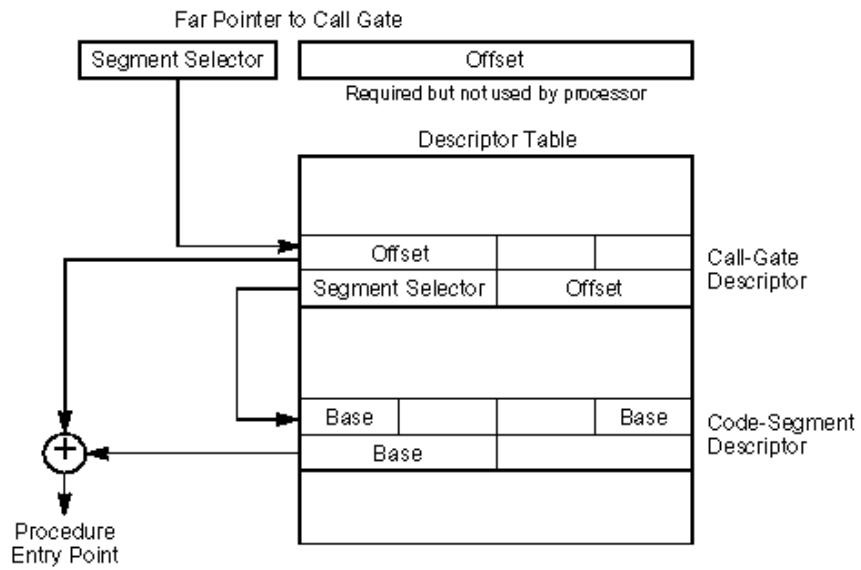

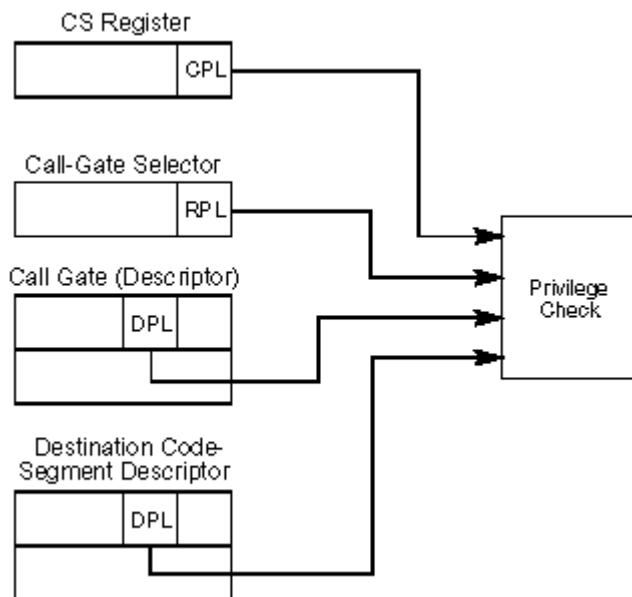

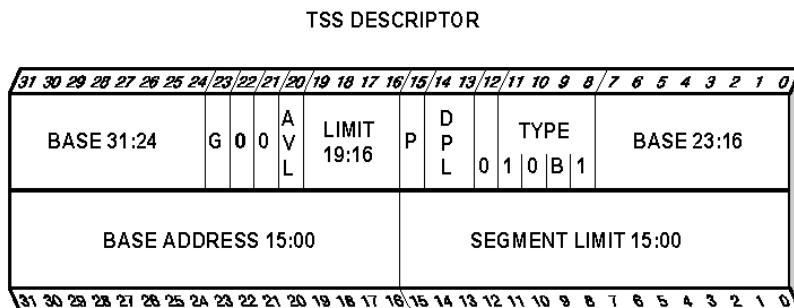

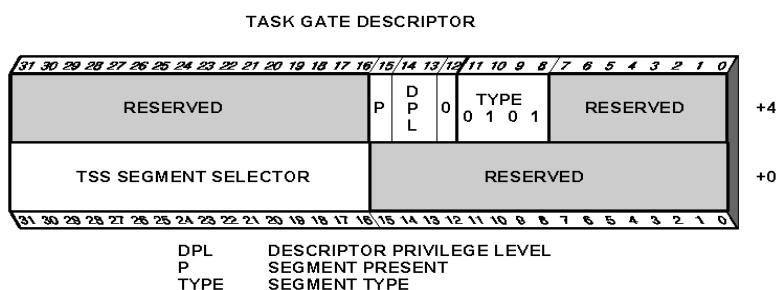

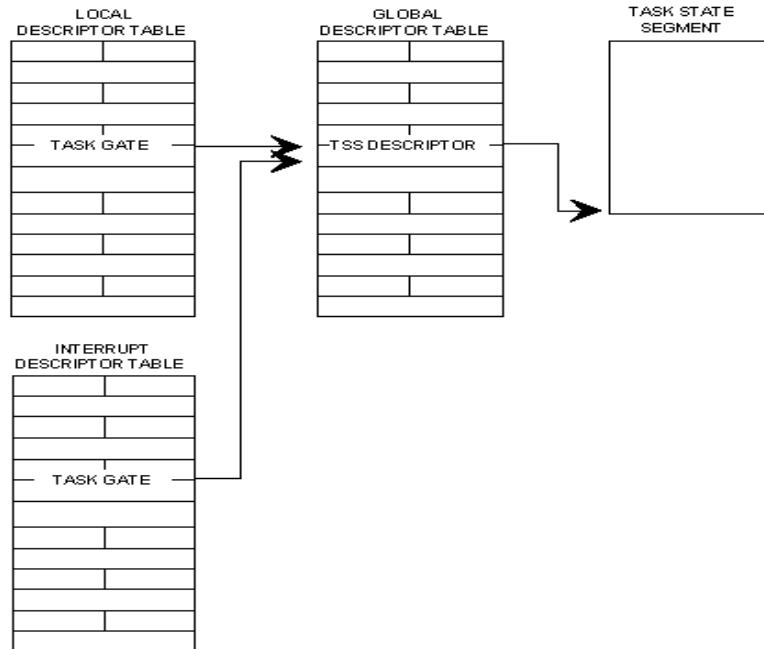

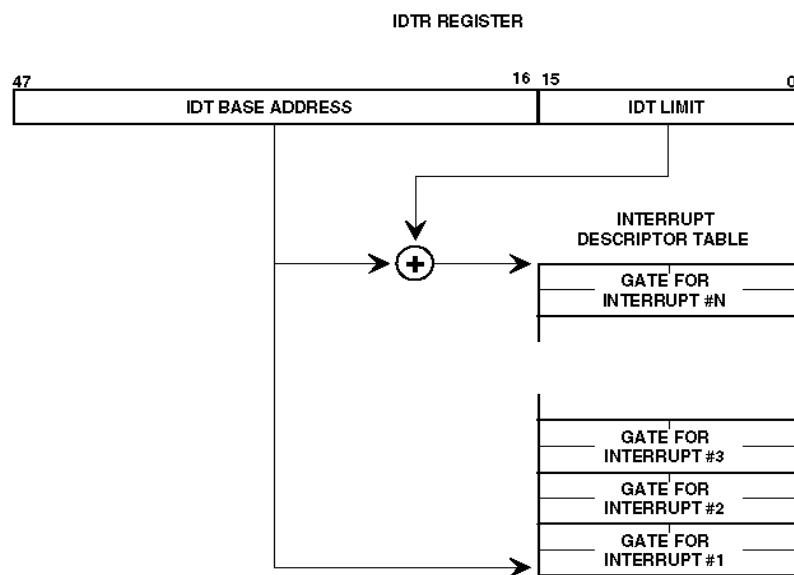

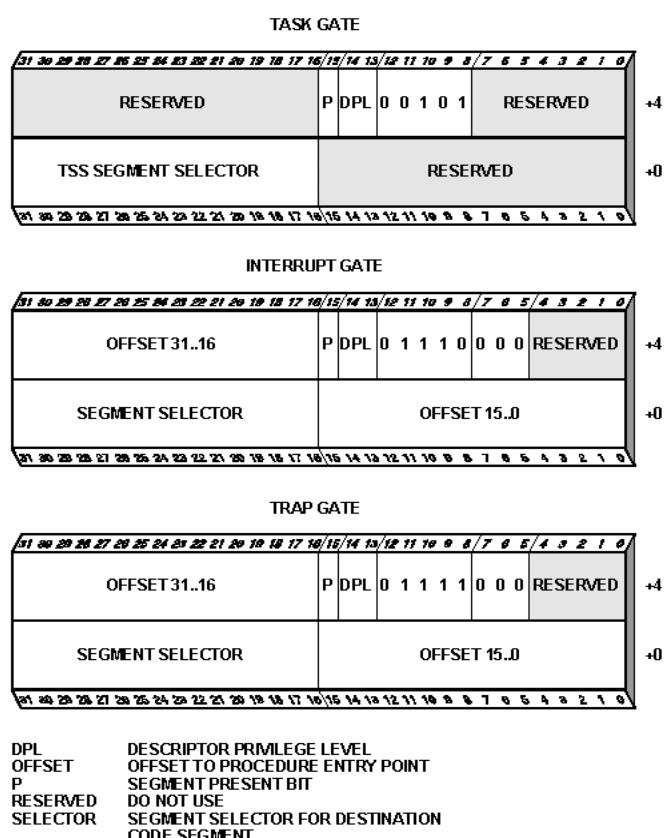

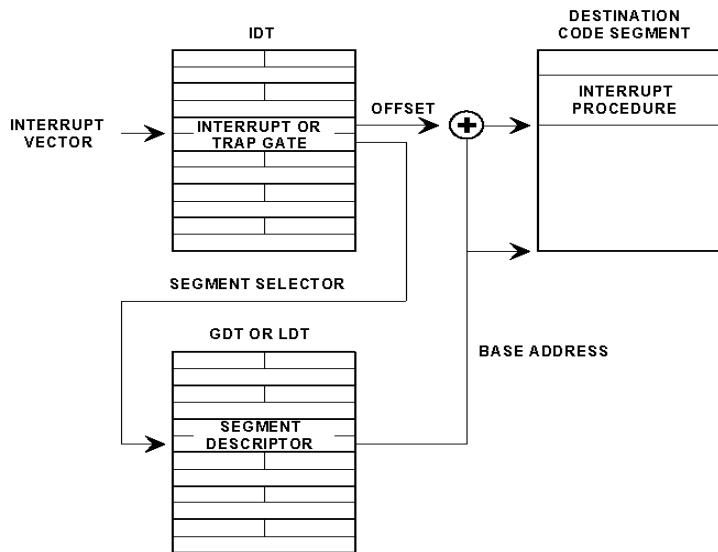

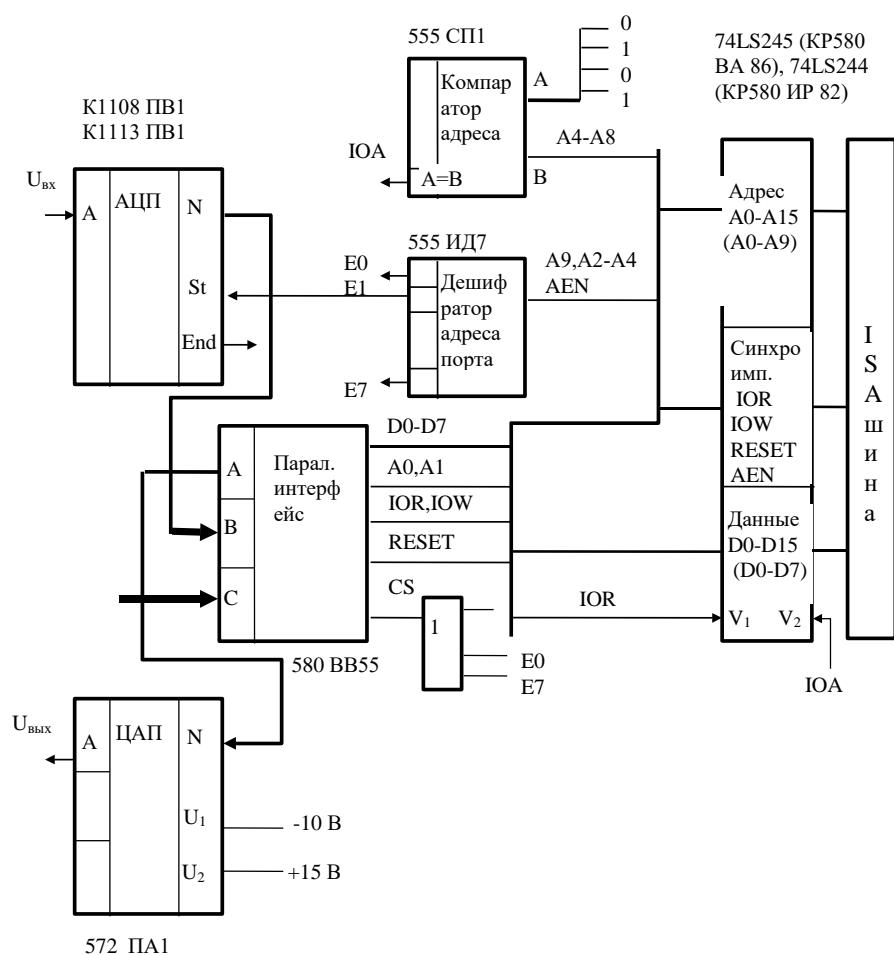

### **Сравнение чисел, флаги и набор команд ветвления**