Федеральное агентство по образованию

---

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

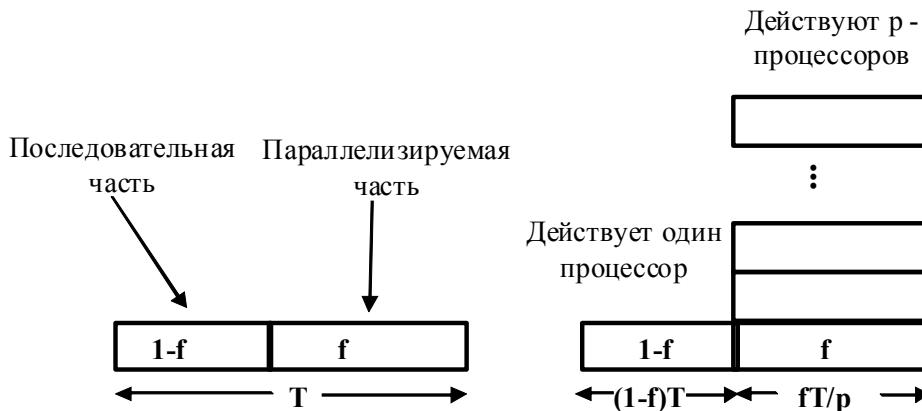

ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

---

*С. А. МОЛОДЯКОВ*

**АРХИТЕКТУРА ЭВМ**

**Часть 2. Современные процессоры и**

**мультипроцессорные системы. Периферийные**

**устройства**

**УЧЕБНОЕ ПОСОБИЕ**

Санкт-Петербург

Издательство Политехнического университета

2014

УДК 004.2: 004.35: 004.431.4

Молодяков С.А.

Архитектура ЭВМ. Часть 2: учебное пособие. СПб.: Изд. СПбГПУ, 2014.- с.

В учебном пособии представлен материал лекций, которые читаются по дисциплинам «Архитектура ЭВМ» и «ЭВМ и периферийные устройства» на кафедре информационных и управляемых систем СПбГПУ. В первой части пособия рассмотрены вопросы, связанные с базовой организацией ЭВМ, а также ее программирования на языке Ассемблера. Во второй части рассмотрены современные процессоры и мультипроцессорные системы, а также периферийные устройства.

Учебное пособие предназначено для студентов, изучающих дисциплины «Архитектура ЭВМ», «ЭВМ и периферийные устройства» по специальностям 231000 Программная инженерия, 230100 Информатика и вычислительная техника.

Печатается по решению редакционно-издательского совета Санкт-Петербургского государственного политехнического университета.

© Молодяков С. А., 2014

© Санкт-Петербургский государственный

политехнический университет

# Оглавление

|                                                                                                                                                      |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Оглавление.....                                                                                                                                      | 3   |

| Глава 1. Процессоры. Архитектурные пути обеспечения параллельности уровня команд.....                                                                | 5   |

| 1.1. Пути повышения производительности .....                                                                                                         | 5   |

| 1.2. Способы оценки производительности средств вычислительной техники .....                                                                          | 9   |

| 1.3. Архитектуры реализации параллельности выполнения команд. Конвейеризация. Суперскалярная архитектура. Процессоры с длинным командным словом..... | 12  |

| 1.4. Структурные конфликты, зависимости по данным и по управлению.....                                                                               | 15  |

| 1.4.1. Структурные конфликты .....                                                                                                                   | 15  |

| 1.4.2. Конфликты по данным и методы их преодоления.....                                                                                              | 16  |

| 1.4.3. Конфликты по управлению .....                                                                                                                 | 19  |

| 1.4.4. Проблемы реализации точного прерывания в конвейере.....                                                                                       | 21  |

| 1.4.5. Статическое и динамическое предсказание переходов .....                                                                                       | 22  |

| 1.4.6. Параллелизм на уровне выполнения команд .....                                                                                                 | 27  |

| 1.4.7. Методы ускорения переключения контекста процессора.....                                                                                       | 32  |

| 1.5. Аппаратная поддержка суперскалярных процессоров.....                                                                                            | 32  |

| 1.6. Архитектура машин с длинным командным словом.....                                                                                               | 36  |

| Глава 2. Архитектуры процессоров.....                                                                                                                | 39  |

| 2.1. Intel процессоры с архитектурой 80x86, Pentium .....                                                                                            | 39  |

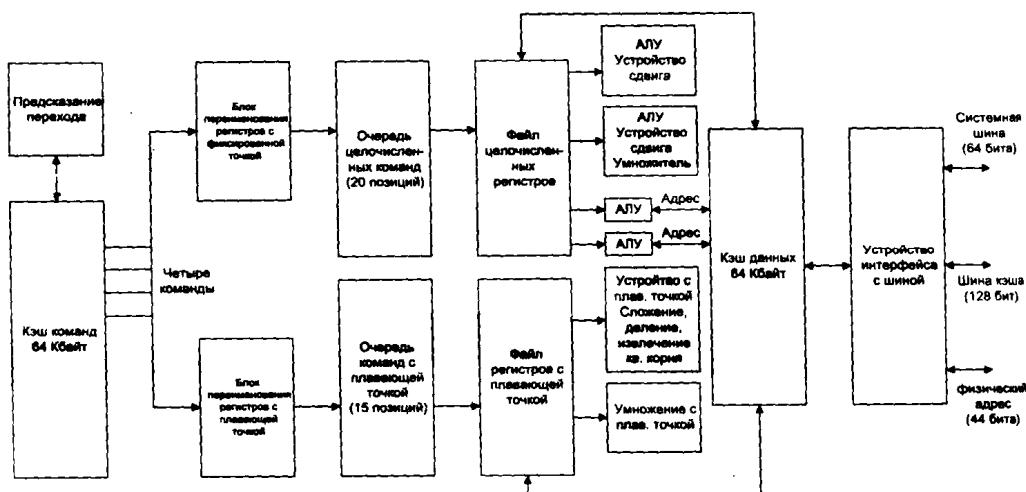

| 2.1.1. Процессор Pentium (архитектура P5).....                                                                                                       | 39  |

| 2.1.2. Режим системного управления SMM (System Management Mode) .....                                                                                | 45  |

| 2.1.3. Процессор Intel Atom .....                                                                                                                    | 47  |

| 2.1.4. Процессор Pentium MMX Pentium .....                                                                                                           | 48  |

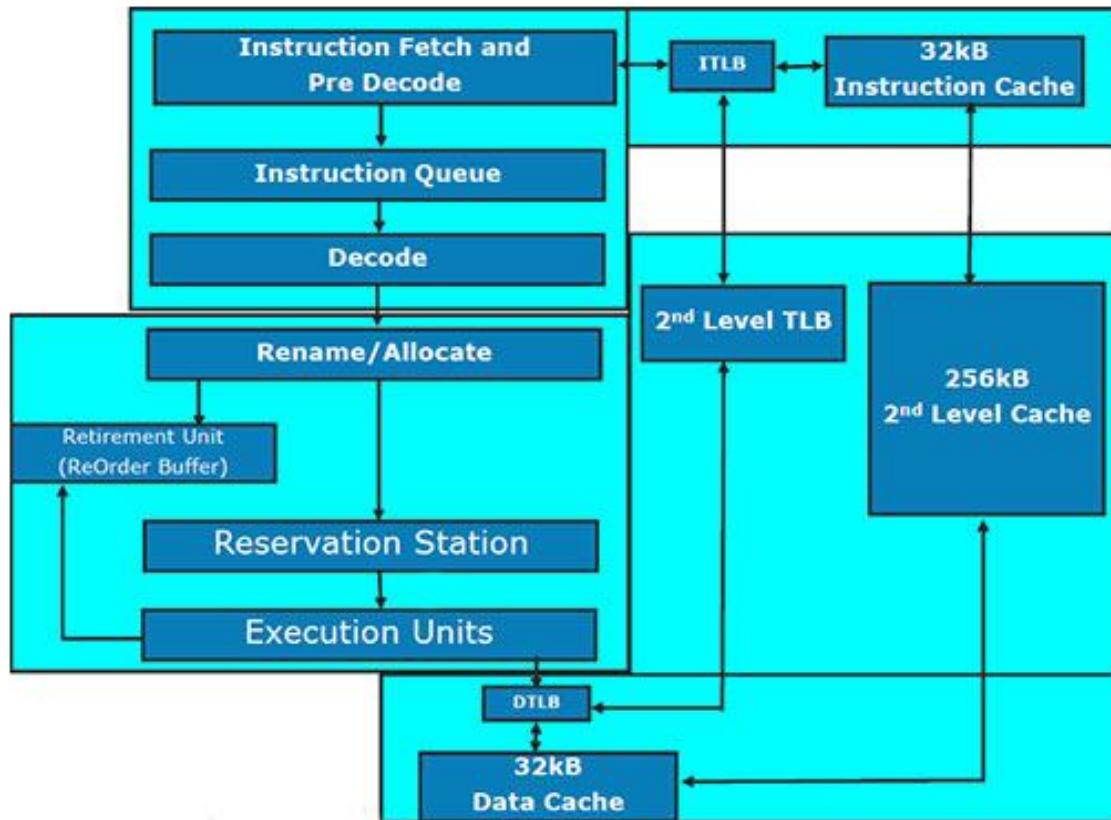

| 2.1.5. Процессоры Pentium-Pro, Pentium II, Pentium III (архитектуры P6).....                                                                         | 50  |

| 2.1.6. Процессор Pentium 4 .....                                                                                                                     | 61  |

| 2.1.7. Архитектура Core i7 .....                                                                                                                     | 71  |

| RISC процессоры .....                                                                                                                                | 73  |

| 2.2. Микропроцессоры с архитектурой Alpha .....                                                                                                      | 73  |

| 2.3. Микропроцессоры с архитектурой PowerPC .....                                                                                                    | 76  |

| Процессоры с длинным командным словом .....                                                                                                          | 89  |

| 2.5. Микропроцессоры с архитектурой Itanium.....                                                                                                     | 89  |

| 2.6. Микропроцессоры для мобильных платформ с архитектурой Transmeta Crusoe                                                                          | 95  |

| Глава 3. Мультипроцессорные системы.....                                                                                                             | 100 |

| 3.1. Уровни параллелизма. Гранулярность.....                                                                                                         | 100 |

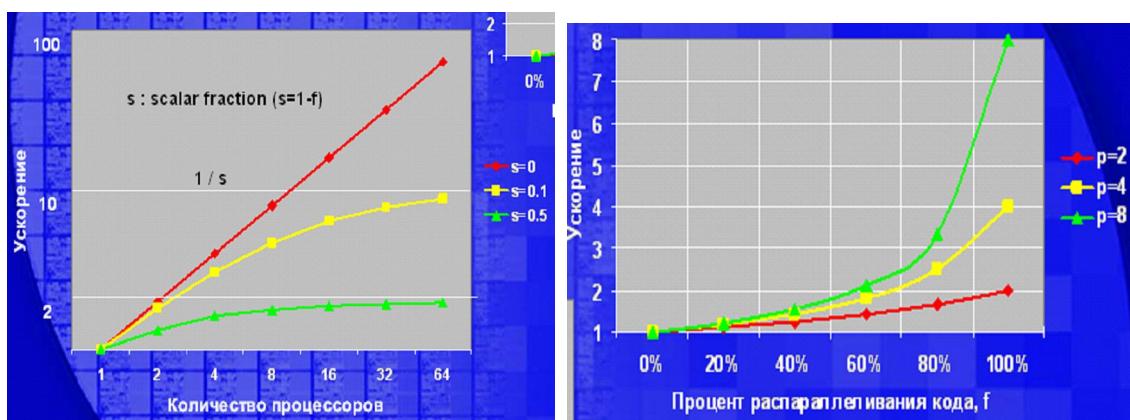

| 3.2. Закон Амдала .....                                                                                                                              | 101 |

| 3.3. Информационные модели.....                                                                                                                      | 103 |

| 3.4. Классы параллельных архитектур. Классификация Флинна .....                                                                                      | 104 |

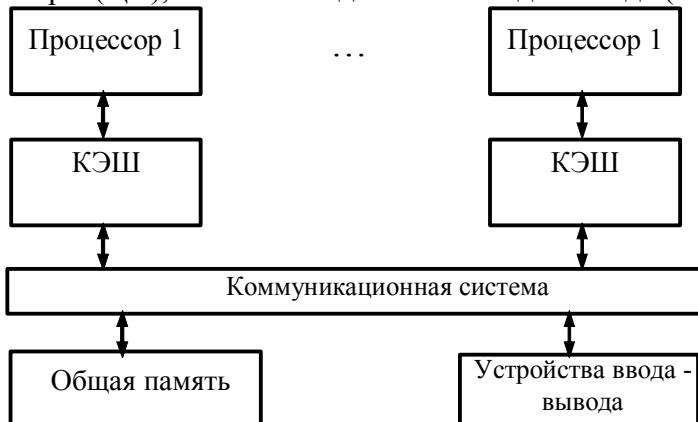

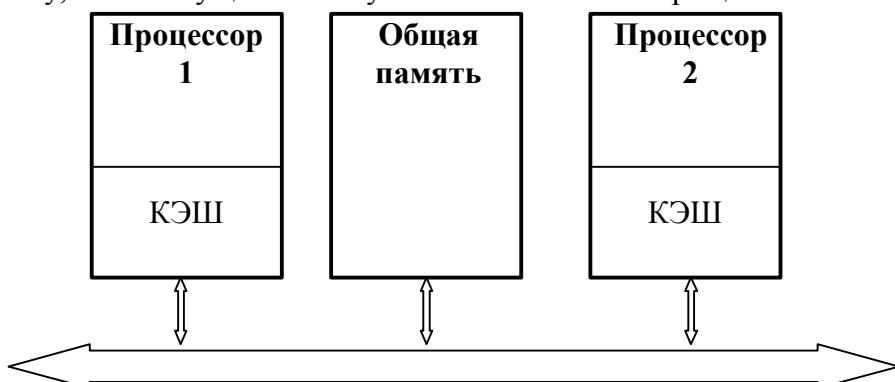

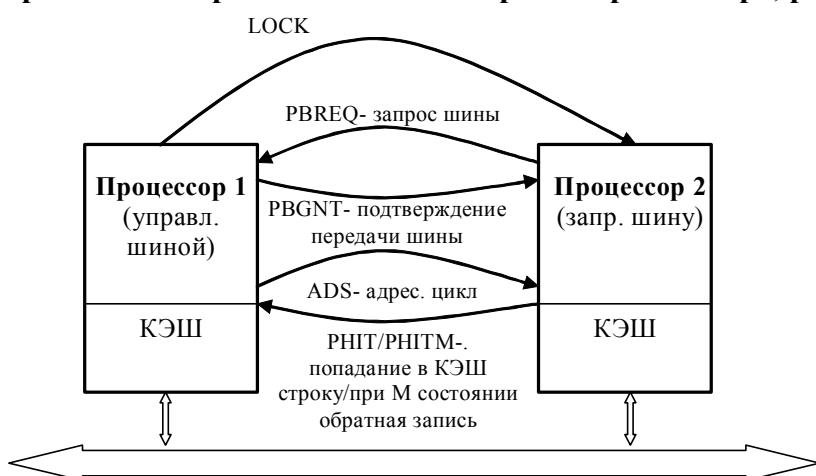

| 3.5. Мультипроцессоры UMA с шинной организацией.....                                                                                                 | 109 |

| 3.6. Мультипроцессоры NUMA (nonuniform memory access) .....                                                                                          | 115 |

| 3.7. MPP архитектура. Сеть процессоров .....                                                                                                         | 120 |

| 3.8. Кластеризация.....                                                                                                                              | 131 |

| 3.9. Нейронная сеть (нейропроцессоры).....                                                                                                           | 135 |

| 3.10. Процессоры с многозначной (нечеткой) логикой.....                                                                                              | 143 |

|                                                                    |     |

|--------------------------------------------------------------------|-----|

| Часть 4. Дискретизация аналогового сигнала. Кодирование звука..... | 145 |

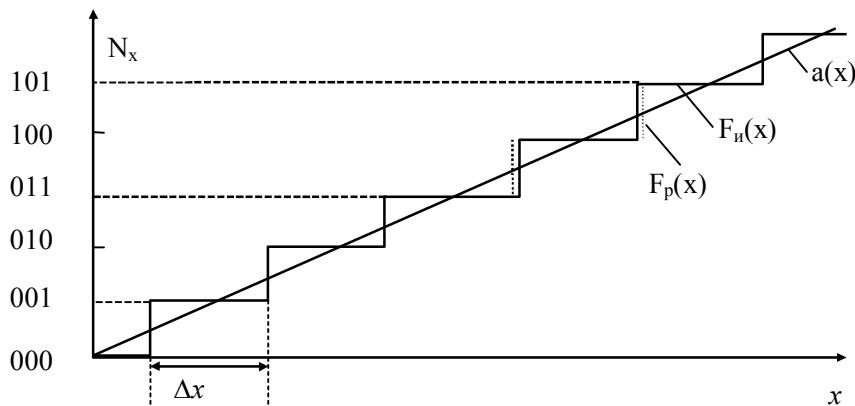

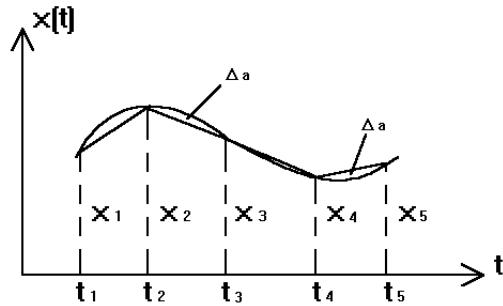

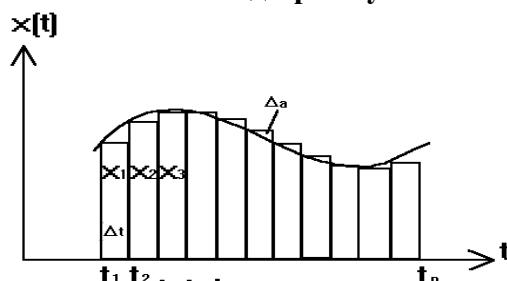

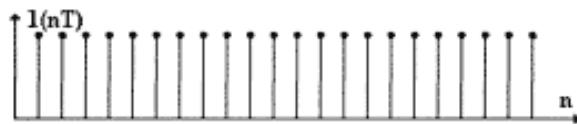

| 4.1. Дискретизация аналогового сигнала.....                        | 145 |

| 4.2. Ошибки дискретизации. Погрешности преобразования.....         | 146 |

| Динамическая погрешность.....                                      | 150 |

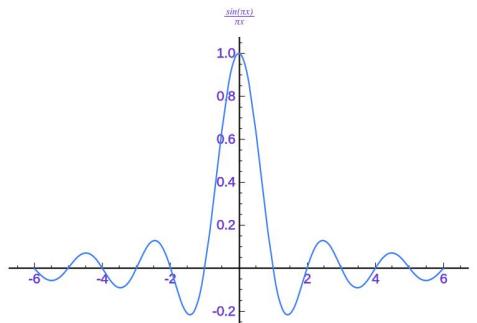

| 4.3. Теорема Котельникова. Эффекты дискретизации.....              | 152 |

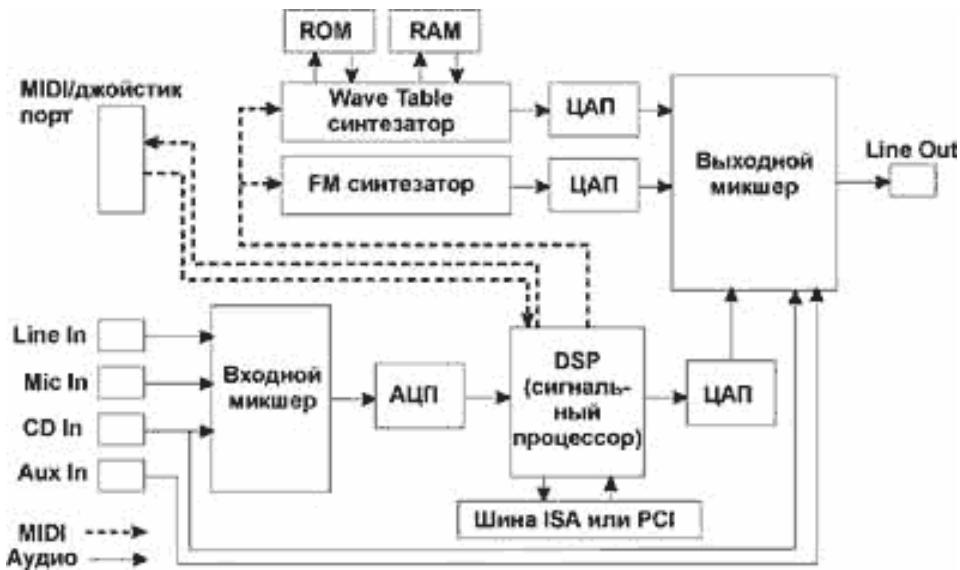

| 4.4. Организация Sound blaster.....                                | 156 |

| 4.5. Форматы файлов представления звука .....                      | 160 |

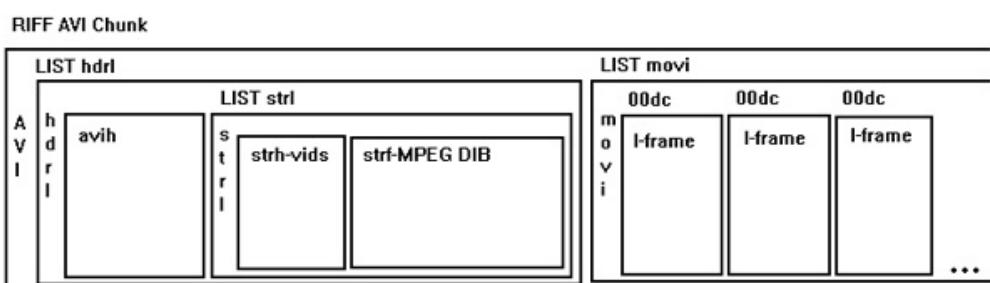

| 4.5.1. Форматы контейнеров RIFF .....                              | 160 |

| 4.5.2. Формат WAV файла.....                                       | 161 |

| 4.5.3. Формат контейнера AVI .....                                 | 162 |

| 4.5.4. Контейнер MKV .....                                         | 163 |

| 4.5.5. Формат MP3 .....                                            | 164 |

| 4.5.6. Форматы Ogg Vorbis и WMA .....                              | 168 |

| 4.6. Библиотеки программ для проигрывания звуковых файлов.....     | 168 |

| 4.6.1. DirectSound .....                                           | 169 |

| 4.6.2. Библиотека FMOD .....                                       | 172 |

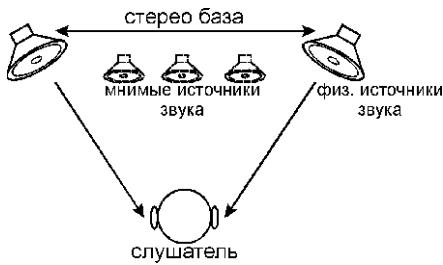

| 4.7. 3d звук .....                                                 | 176 |

| Часть 5. Фотоприемники и видеосистемы.....                         | 179 |

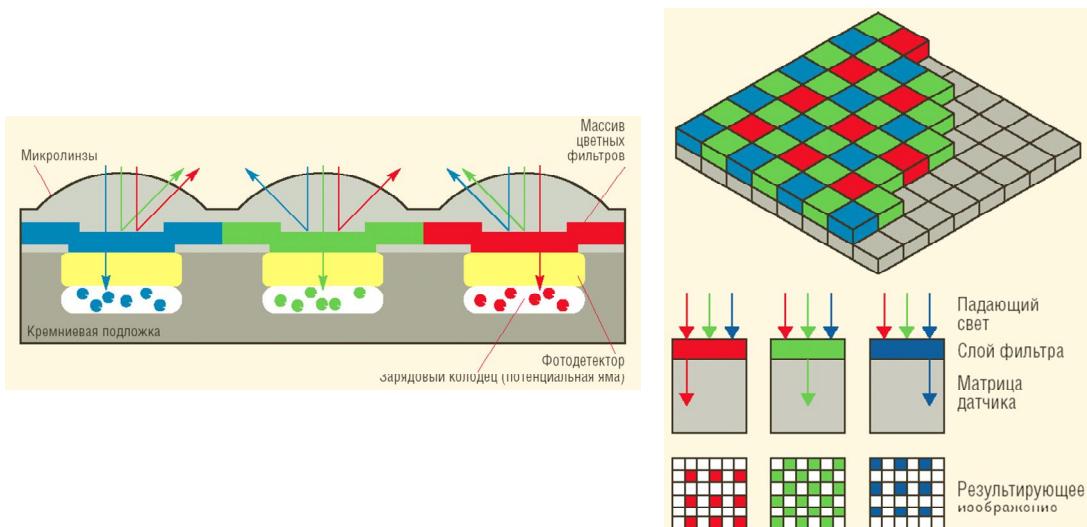

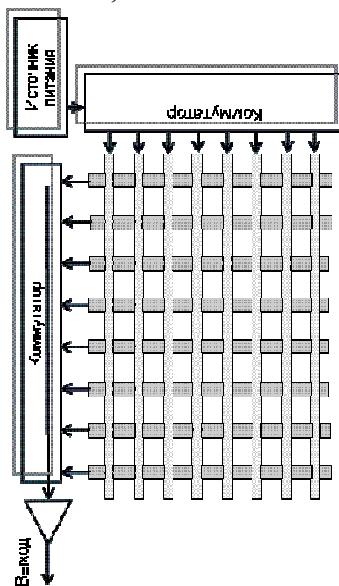

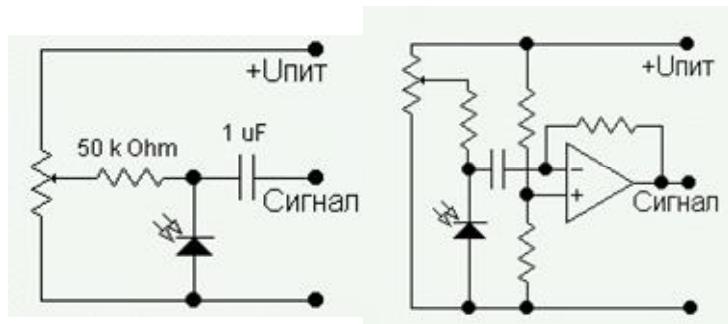

| 5.1.Фотоприемники на приборах с зарядовой связью.....              | 179 |

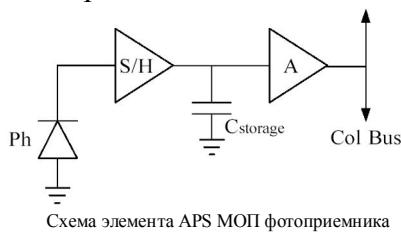

| 5.2. КМОП-фотоприемники .....                                      | 190 |

| 5.3. Системы технического зрения.....                              | 193 |

| 5.4. Video Blaster. Web-камера .....                               | 194 |

| 5.5. Библиотеки для работы с видеосистемами.....                   | 197 |

| Часть 6. Средства вывода информации. Интерфейсы.....               | 200 |

| 6.1. Принтеры.....                                                 | 200 |

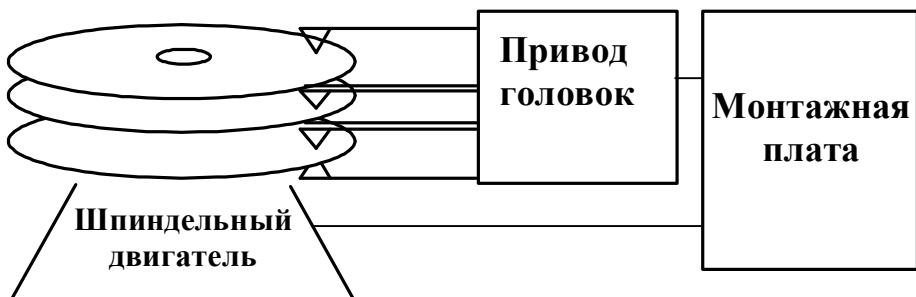

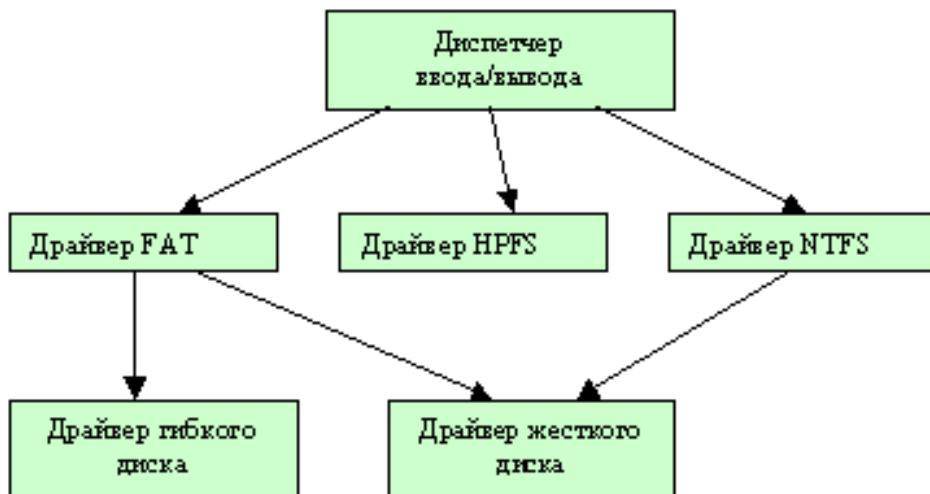

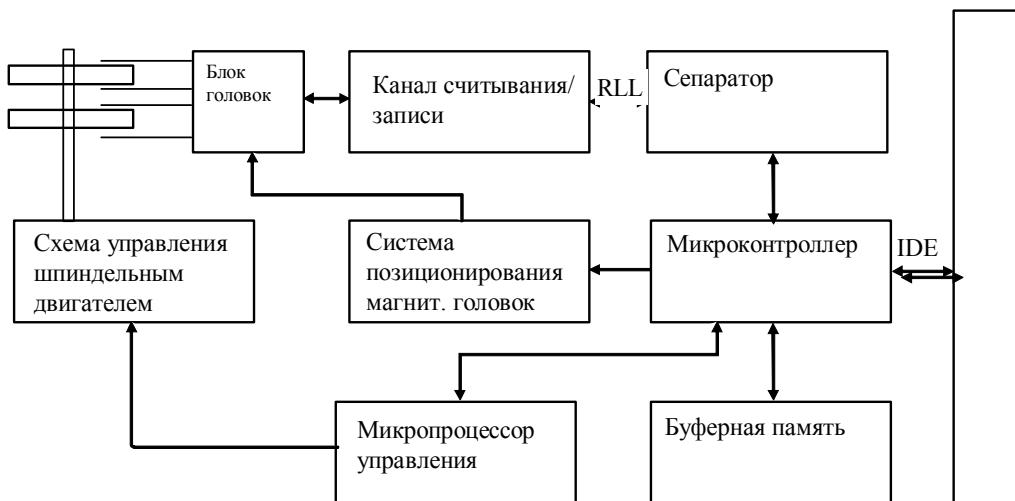

| 6.2. Магнитные диски.....                                          | 206 |

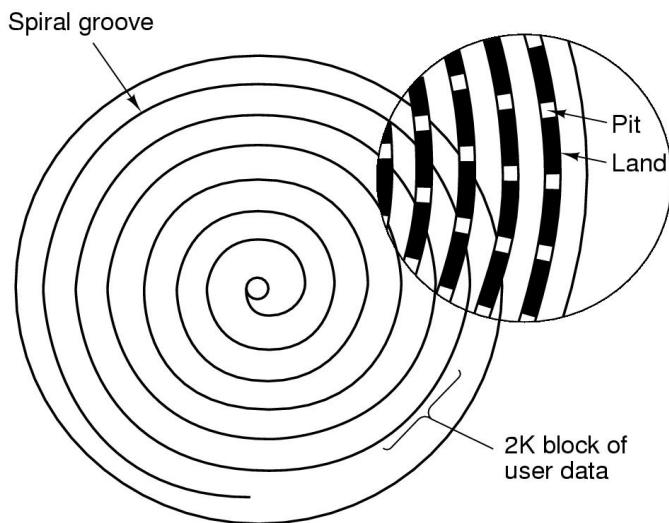

| 6.3. Оптические диски .....                                        | 213 |

| 6.4. Интерфейсы.....                                               | 219 |

| Заключение .....                                                   | 231 |

| Библиографический список .....                                     | 232 |

# Глава 1. Процессоры. Архитектурные пути обеспечения параллельности уровня команд

## 1.1. Пути повышения производительности

Повышение производительности компьютера и вычислительной системы связано с тремя элементами:

- Повышение тактовой частоты процессора.

- Увеличение пропускной способности подсистемы памяти.

- Повышение степени параллелизма вычислений в компьютере/вычислительной системы.

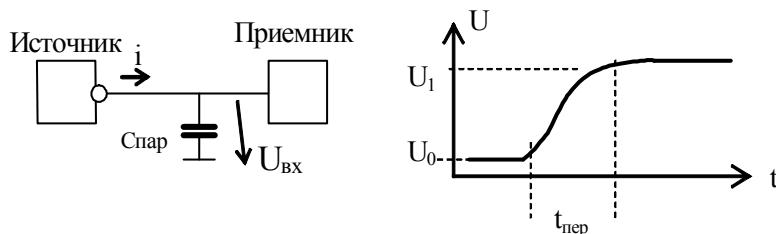

**Повышение тактовой частоты** в первую очередь определяется успехами технологии. Сегодня практически все производители используют технологию КМОП. Максимальная частота работы процессора связана в основном с процессом перезаряда паразитных емкостей. Величина паразитных емкостей определяется проектными нормами (минимальным размером элемента на кристалле). Уменьшение проектных норм приводит одновременно к уменьшению требуемых напряжений питания, уменьшению мощности, потребляемой одним логическим вентилем и к уменьшению времени переключения вентиля. Основное соотношение для экстенсивного увеличения скорости определяется выражением:

$$t_{\text{пер}} = k \Delta U_{01} L_{\text{пр}} / \sqrt{P}$$

где  $t_{\text{пер}}$  - время переключения сигнала с одного уровня на другой (см. рис.);

$\Delta U_{01}$  – диапазон переключения;

$L_{\text{пр}}$  – проектная норма, паразитная емкость пропорциональна квадрату величины проектной нормы  $C_{\text{пар}} \sim \epsilon^* L_{\text{пр}}^2 / d$

$P$  – мощность переключения.

Из этой (качественной) формулы видно, каким путем и за какую цену можно повышать быстродействие. Время переключения элемента будет тем меньше, чем меньше промежуток  $\Delta U_{01}$  между интервалами сигнала (напряжения), кодирующими значения логической переменной, чем меньше проектные нормы  $L_{\text{пр}}$  (размеры элементов на кристалле) и чем больше мощность  $P$ , потребляемая логическим элементом от источника питания, и затрачиваемая на перезаряд паразитных емкостей и в конечном итоге, нагревающая кристалл БИС.

В настоящее время одним из основных показателей эффективности процессора является величина, показывающая производительность на единицу затраченных ресурсов. Такой величиной служит, например величина (МГц/Ватт).

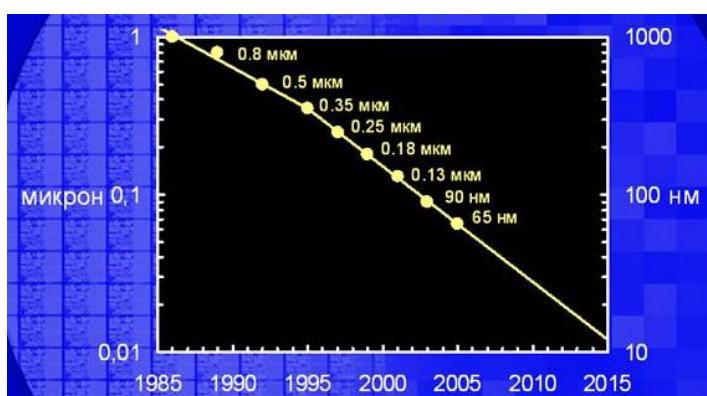

Технологический предел линейных размеров транзисторов на кристалле, обусловленный физическими ограничениями. На пути дальнейшей миниатюризации кроме физических ограничений имеются и экономические. Для каждого следующего

поколения микросхем стоимость технологии удваивается. Технология развивается в направлении увеличения плотности транзисторов на кристалле, роста числа слоев металлизации и повышения тактовой частоты наряду с уменьшением напряжения питания и удельной (на один транзистор) потребляемой электрической и выделяемой тепловой энергии. С каждым поколением линейные размеры элементов уменьшаются в 0.7 раза. Смена поколений микропроцессоров происходит каждые 2-3 года. Увеличение числа слоев металлизации экспоненциально повышает процент брака при производстве, увеличение площади кристалла также приводит к снижению выхода годных кристаллов.

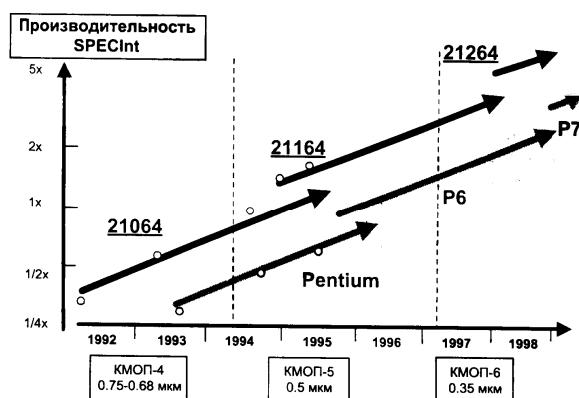

На рис.1.1 показан график уменьшения характерного размера проектной нормы в компании Intel. На рис.1.2 приведена эволюция технологии в компании Intel. Компания вводит новую технологию каждые два года. Видно, что происходит непрерывное повышение тактовых частот.

Рис.1.1. График уменьшения характерного размера проектной нормы в компании Intel.

| Процесс        | P1262 | P1264 | P1266 | P1268 |

|----------------|-------|-------|-------|-------|

| Литография     | 90 нм | 65 нм | 45 нм | 32 нм |

| Начало произв. | 2003  | 2005  | 2007  | 2009  |

Рис.1.2. Эволюция технологии в компании Intel.

### Ограничение Лэндауэра

При необратимом процессе обработки информации, когда возможна потеря битов, затраты на обработку одного бита не могут быть меньше величины  $kT \ln 2$ , где:  $k$  — константа Больцмана, а  $T$  — температура по Кельвину

Обработка одного бита — это результат выполнения какой-либо операции над двумя битами (AND, OR, XOR). Можно считать, что при выполнении операции один из битов-операндов превращается в результат операции и энергия не теряется, а вот другой бит-операнд теряется. Энергия выделяется в виде тепла, что и считается минимальной энергетической платой за выполнение элементарной операции.

Технологиям в 22 нм соответствует уровень энергетических затрат на обработку одного бита не менее 100 000 – 1 000 000  $kT$ , и Лэндаэр, исследуя динамику улучшения технологий, показал, что достижение уровня  $kT$  произойдет в районе 2020 года (5 нм).

Закон Мура перестанет работать не позднее 2024 года

## **Иновации, не масштабирование – ключ к развитию микроэлектроники**

Таково мнение док. Бернарда Мейерсона – вице-президента по стратегическим альянсам и директора по технологиям компании IBM. Вскоре промышленность уже не сможет улучшать производительность систем за счет увеличения рабочей частоты, поскольку, чем выше рабочая частота и уровень интеграции, тем больше потребляемая мощность приборов, уже сегодня достигающая своего предела. Чтобы увеличить производительность необходимы новые принципы построения компонентов, схем и их архитектуры.

По мнению Мейерсона, в истории развития полупроводниковой электроники можно выделить две поворотные точки. В 60–70-е годы на первых этапах микроэлектроники разработчики продвигали биполярную технологию и сумели довести число транзисторов на кристалле до десятков тысяч. Дальнейшее увеличение плотности элементов столкнулось с проблемой слишком возросших энергозатрат. Но к этому времени уже появилась КМОП-технология, обещавшая улучшить характеристики и степень интеграции микросхем, выполненных на ее основе. И все это при меньшей потребляемой мощности. Поэтому с 70-х годов разработчики непрерывно увеличивают число вентилей на кристалле и улучшают их характеристики. Однако сегодня КМОП-микросхемы так же "голодают", как и их ранние биполярные "сестры". Современная микроэлектроника, считает Мейерсон, подошла ко второй поворотной точке в своей истории, хотя сейчас нет новой технологии, которая позволила бы в ближайшем будущем заменить КМОП микросхемы. Такие перспективные устройства, как приборы на углеродных нанотрубках появятся лишь через 10–15 лет.

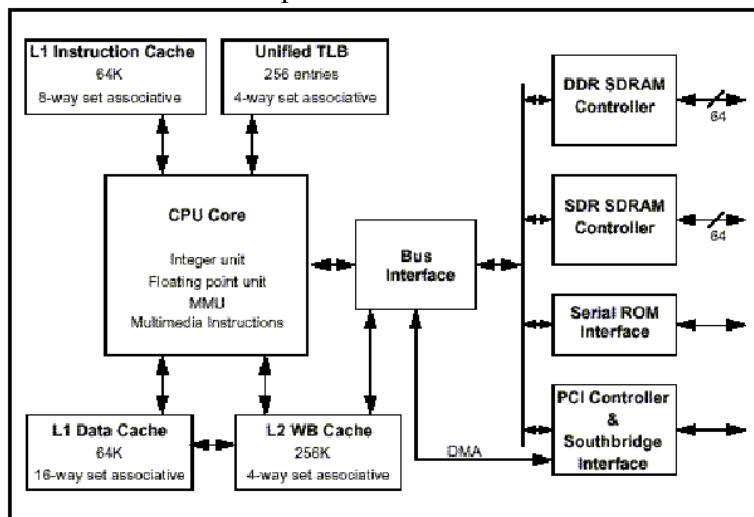

**Увеличение пропускной способности подсистемы памяти** достигается сбалансированным выбором многоуровневой структуры КЭШ-памяти и пропускной способности шин между этими уровнями. Следует помнить, что эффективность использования (быстрой) кэш-памяти основана на принципе «один раз медленно из основной памяти в кэш, а затем много раз быстро из кэша в процессор». Иерархическая структура памяти рассмотрена в части 1 пособия.

В зависимости от специфики конкретной программы эффективность кэша может варьировать от очень высокой – 5...10 кратное ускорение (для задач с малым объемом кода и данных, которые целиком помещаются в кэш и с высокой степенью их повторного использования – типичный пример –итеративная вычислительная задача) до отрицательной, когда значительная часть данных (чаще) или кода (реже) используется лишь однократно.

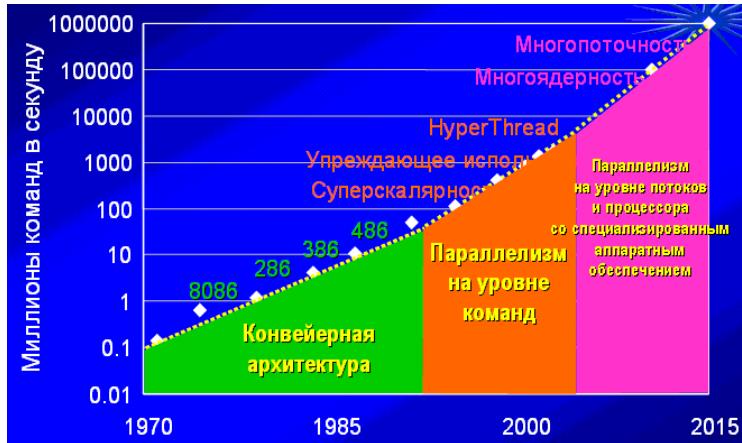

**Повышение степени параллелизма вычислений в компьютере** в первую очередь связано с появлением дополнительных элементов (транзисторов) на кристалле, которые возникли за счет успехов в технологии. Стало возможным использовать и развивать различные пути обеспечения параллельности уровня команд и уровня потоков команд. Появляются новые архитектуры процессоров. Можно выделить два этапа развития архитектуры процессора:

- Развития архитектуры ядра процессора. Суперскалярность и конвейерность.

- Развития многоядерных архитектур.

В данной части и следующей рассмотрим проблемы и направления развития процессора, которые обеспечивают параллельное выполнение команд и их этапов в процессоре. Многоядерность позволяет не только параллельно выполнять потоки команд, но и снижает потребляемую процессоров мощность. Это является основным

направлением развития архитектур быстродействующих процессоров. Многоядерные архитектуры будут рассмотрены далее при описании многопроцессорных систем.

На рис.1.3. показано развитие параллелизма в рамках единого процессора на примере процессоров Intel x86.

Рис. 1.3. Развитие параллелизма в рамках единого процессора Intel x86.

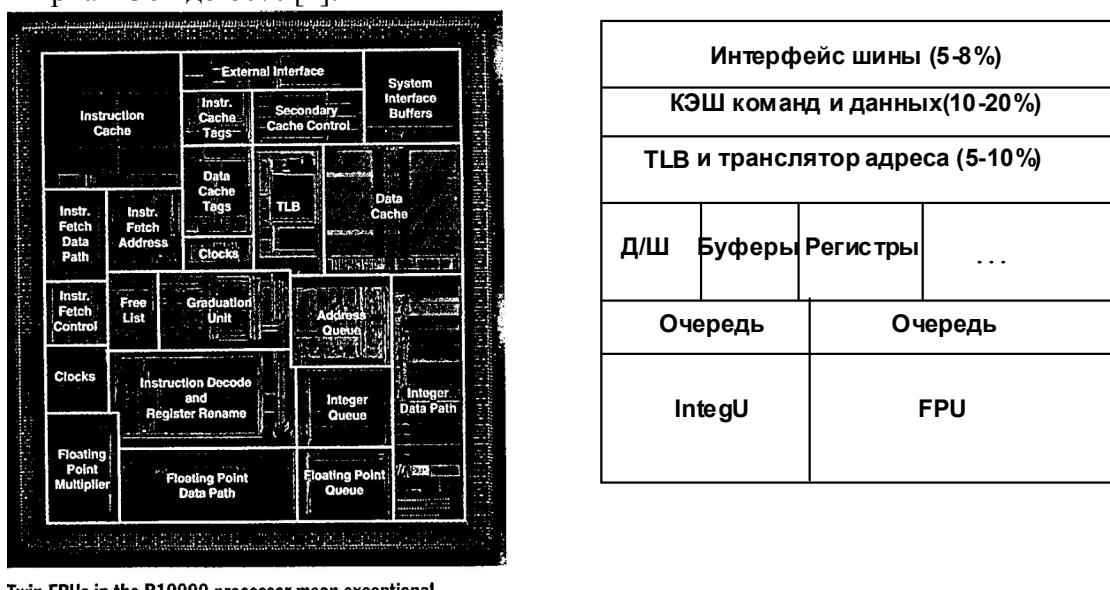

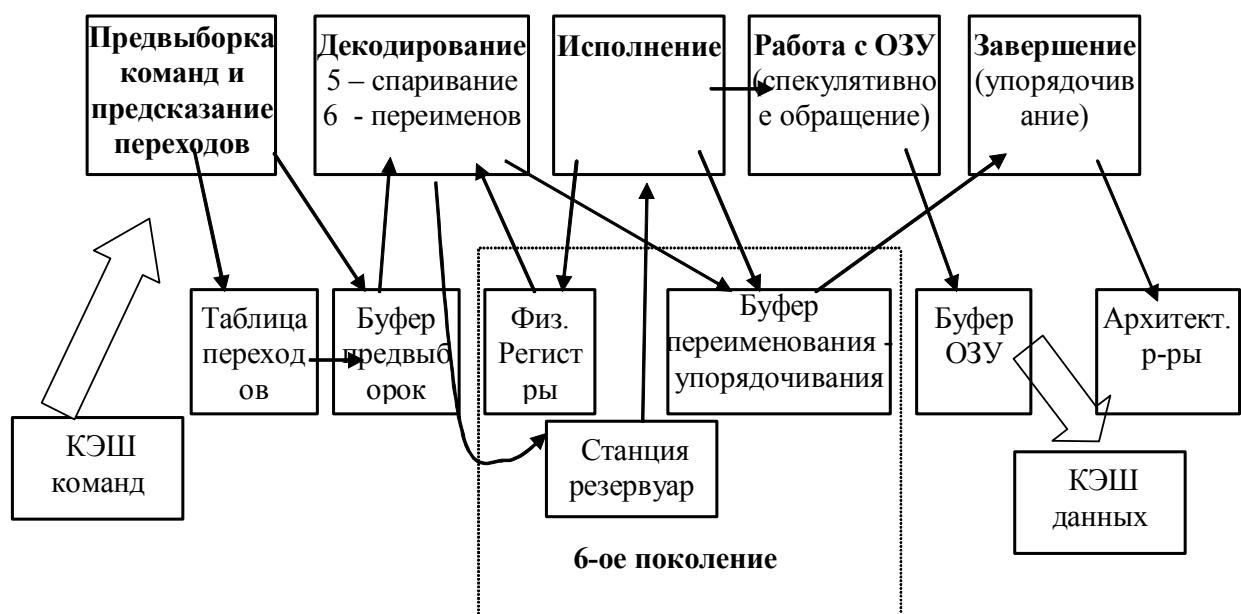

С каждым поколением микропроцессоров все меньшую долю поверхности кристалла занимают исполнительные элементы (само вычислительное ядро) и большую часть можно отдать на дополнительные к ядру элементы. Специализация современных микропроцессоров сводится к специализации этих элементов. Так в универсальных микропроцессорах дополнительные площади поверхности кристалла отдаются под КЭШ память, а в микроконтроллерах - под коммуникационные и другие устройства. На рис. 1.4 приведен пример распределения поверхности кристалла для процессора R10000 (Процессор 5-го поколения; 64 регистра целочисленных+64 регистра чисел с плавающей запятой; каждый регистр 64 разряда; число конвейеров – 5). В процессорах шестого поколения доля КЭШ первого и второго уровня возрастает: в Pentium4 до 40%, а в Alpha21364 до 80% [1].

Twin FPU in the R10000 processor mean exceptional

Рис.1.4. Пример распределения транзисторов процессора R10000

## 1.2. Способы оценки производительности средств вычислительной техники

Производительность средства ВТ (компьютера) можно оценивать различными способами. В таблице 7.1. приведены способы, в разной степени учитываяющие влияние на производительность «окружения» процессора. В первом (грубом) приближении принято считать, что производительность определяется скоростью (тактовой частотой) процессора. Однако, суперскалярные процессоры выполняют более одной операции за такт, поэтому более точным показателем возможности процессора выполнять команды, является пиковая производительность. В этом случае для суперскалярного процессора с тактовой частотой 1МГц, выполняющего 3 операции за такт, пиковая производительность составит 3 MIPS или 3MFLOPS. (MFLOPS = MFlop/sec. - миллионы операций с плавающей точкой в секунду).

Табл 7.1. Разные способы оценки производительности/эффективности

| N  | Способ оценки                                   | Влияющие факторы                                                                                                                                   |

|----|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Время переключения элементов                    | Скорость переключения транзисторов и скорость перезаряда паразитных емкостей                                                                       |

| 2. | Тактовая частота – пиковая производительность   | Логическая «глубина» тактируемых слоев                                                                                                             |

| 3. | Времена выполнения команд                       | Аппаратная/ микропрограммная реализация                                                                                                            |

| 4  | Интенсивность потока результатов на выходе АЛУ  | Степень конвейеризации/ запараллеливания команд, зависимости (dependencies), относительная частота использования команд                            |

| 5. | Benchmarks (тестовые последовательности команд) | Относительное быстродействие подсистем: процессора, а также слоев памяти                                                                           |

| 6. | Тестовые задачи                                 | Быстродействие дисковой и видео подсистем, а также организационная сторона и взаимодействие с объектами вне ВС (оператор, объект управления, сеть) |

Для полной оценки производительности ЭВМ используются системы тестов. В целом выделяют тесты разработчиков и тесты потребителей.

Один из распространенных тестов при оценке быстродействия ЭВМ – это тест/индекс Intel iCOMP(Intel COMPatible Microprocessor Performance). Этот тест - индекс в 1992г. фирма Intel предложила для оценки производительности своих процессоров; тест содержит 67% операций с 16-разрядными целыми числами, 25% - с 32-разрядными целыми числами, 5% - с 32-разрядными действительными числами и 3% - с 16-разрядными действительными числами

SPEC (Standard Performance Evaluation Corporation) - это корпорация, созданная в 1988 году, объединяющая ведущих производителей вычислительной техники и программного обеспечения. SPEC имеет целью разработку и стандартизацию методов оценки производительности современных компьютеров. Разработанные SPEC тестовые пакеты являются де-факто стандартами для оценки производительности современных микропроцессоров, компьютеров и системного ПО.

SPEC выполняет две основные функции: Разрабатывает тестовые пакеты. Собирает и публикует официальные результаты тестов. Корпорация разработала целый ряд тестов для разных систем. Выделим только тестовый пакет для оценки производительности микропроцессоров (ЦП) и вычислительных систем - CPU2000.

Пакет CPU2000 состоит из двух групп тестов - CINT2000 для оценки производительности на целочисленных операциях и CFP2000 для оценки производительности на операциях с плавающей точкой. Группы тестов CINT2000 и CFP2000 ориентированы на оценку работы микропроцессоров, подсистемы кэш-памяти и оперативной памяти, а также компиляторов. Эти тесты не имеют отношения к оценке производительности сети, дисков или графической подсистемы.

В набор CINT2000 входят 11 тестовых приложений, написанных на языке C, и один тест (252.eon) на C++.

| Название    | Краткое описание задачи                                           |

|-------------|-------------------------------------------------------------------|

| 164.gzip    | Утилита сжатия данных (gzip)                                      |

| 175.vpr     | Приложение для расчета FPGA-кристаллов                            |

| 176.gcc     | Компилятор C                                                      |

| 181.mcf     | Приложение для решения задачи потока минимальной стоимости в сети |

| 186.crafty  | Программа для игры в шахматы                                      |

| 197.parser  | Синтаксический разбор для естественного языка                     |

| 252.eon     | Трассировка лучей                                                 |

| 253.perlbmk | Интерпретатор языка Perl                                          |

| 254.gap     | Вычислительная задача из теории групп                             |

| 255.vortex  | Объектно-ориентированная база данных                              |

| 256.bzip2   | Утилита сжатия данных (bzip2)                                     |

| 300.twolf   | Задача позиционирования и маршрутизации                           |

В набор CFP2000 входят 14 тестовых приложений, из которых 6 написаны на языке Fortran 77, 4 на языке Fortran 90 и 4 на C++.

| Название     | Краткое описание задачи                                         |

|--------------|-----------------------------------------------------------------|

| 168.wupwise  | Задача квантовой хромодинамики                                  |

| 171.swim     | Гидродинамическая задача моделирования для "мелкой" воды        |

| 172.mgrid    | Многосеточная решалка для трехмерного потенциального поля       |

| 173.applu    | Решение параболических/эллиптических дифференциальных уравнений |

| 177.mesa     | Трехмерная графическая библиотека (Mesa3D)                      |

| 178.galgel   | Гидродинамическая задача: анализ колебательной нестабильности   |

| 179.art      | Моделирование нейронной сети                                    |

| 183.eqquake  | Моделирование землетрясения методом конечных элементов          |

| 187.facerec  | Задача распознавания лиц на графических изображениях            |

| 188.ampp     | Задача вычислительной химии                                     |

| 189.lucas    | Задача теории чисел (проверка простоты)                         |

| 191.fma3d    | Моделирование crash-тестов методом конечных элементов           |

| 200.sixtrack | Моделирование ускорителя элементарных частиц                    |

| 01.apsi      | Атмосферная задача с учетом температуры, ветра и загрязнений    |

Результаты CPU2000 (CINT2000 и CFP2000) предоставляются в вариантах ("метриках"): время выполнения одной итерации теста, количество итераций за фиксированное время. Метрики типа "rate" (SPECint\_rate2000, SPECfp\_rate2000) позволяют оценить суммарный объем вычислений, который компьютер может выполнить за определенное время. Метрики "non-rate" (SPECint2000) оценивают просто "скорость" вычислений.

Тестовые наборы CINT2000 и CFP2000 состоят соответственно из 12 и 14 независимых тестовых программ, каждая из которых дает отдельный показатель производительности. Для усреднения результатов по отдельным тестам в данном тестовом наборе используется среднее геометрическое от нормализованных результатов всех тестов. Для устранения влияния случайных факторов на результаты тестирования, каждый тест прогоняется нечетное число раз (как минимум, 3), результаты по запускам располагаются по возрастанию и в качестве окончательного берется результат из середины ряда ("медианный").

Показатель SPECint2000, например, вычисляется следующим образом:

$$\text{SPECint2000} = \text{RefTime} / \text{MeasuredTime},$$

где RefTime - время исполнения теста на эталонной машине, а MeasuredTime - время исполнения на тестируемой машине. Таким образом, смысл этого показателя - в относительном ускорении по сравнению с эталонной машиной.

### **Linpack benchmark**

Тест используется для оценки производительности мультипроцессорных систем, включая суперкомпьютеры. Он состоит в решении системы линейных арифметических уравнений  $Ax = f$ ,  $A$  – матрица.

Единицей измерения является *1 flop*. Количество операций, необходимое для решения задачи Linpack, известно с самого начала и зависит от ее размерности. Измеряемая характеристика производительности получается как простое частное от деления известного числа операций на время, затраченное на решение задачи .

Имеется версия для тестирования кластерных систем.

### **Business Applications Performance Corporation BAPCo SYSmark® 2007**

BAPCo – это консорциум независимых тестовых лабораторий, разработчиков компьютеров, полупроводниковой техники и программного обеспечения. В настоящее время членами консорциума являются фирмы Adaptec, Amdahl Corporation, Compaq, Dell, Hewlett-Packard, IBM, Intel, Microsoft, Motorola, NEC и издания Federal Computer Week, InfoWorld, VNU Business Publications Limited (UK). <http://www.bapco.com>

Набор тестов SYSmark работает под управлением всех 32-битных операционных систем семейства Windows и, используя настоящие приложения (в состав тестов входит 12 приложений, называемых Internet Content Creation and Productivity), позволяет определить производительность компьютеров в режиме имитации реальной работы. При тестировании используются следующие офисные приложения: CorelDRAW, Microsoft Excel, Dragon Systems NaturallySpeaking Preferred, Corel Paradox 9, Microsoft PowerPoint и Microsoft Word и др., а также приложения для разработки содержимого Web-узлов: MetaCreations Bryce, Adobe Photoshop и др.

Полученные в результате тестирования коэффициенты отражают производительность тестируемого компьютера по отношению к базовой конфигурации.

Помимо уменьшения времени переключения логических элементов, существует фактор, приводящий к увеличению скорости работы процессоров, и за 20 лет, благодаря этому фактору, удалось достичнуть дополнительного увеличения скорости более чем на порядок. Этот дополнительный фактор – совершенствование структуры процессоров, вследствие чего удается строить более быстрые процессоры без увеличения скорости переключения элементов. Основное улучшение связано с параллельностью. Параллельное выполнение команд в ядре процессора обеспечивается двумя процессами: конвейеризацией и параллельным выполнением команд - суперскалярностью.

### **1.3. Архитектуры реализации параллельности выполнения команд. Конвейеризация. Суперскалярная архитектура. Процессоры с длинным командным словом.**

#### **Конвейеризация.**

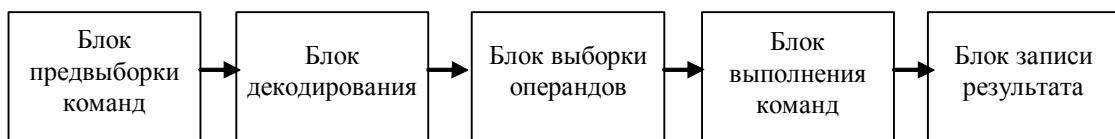

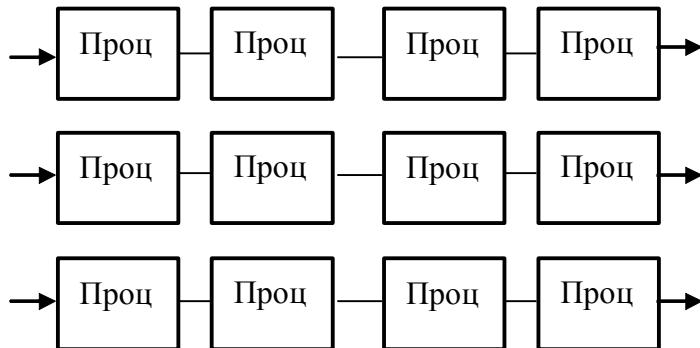

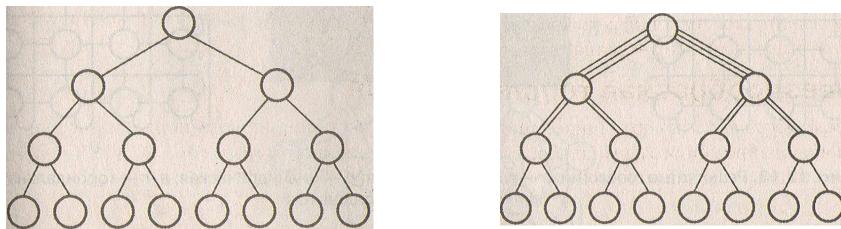

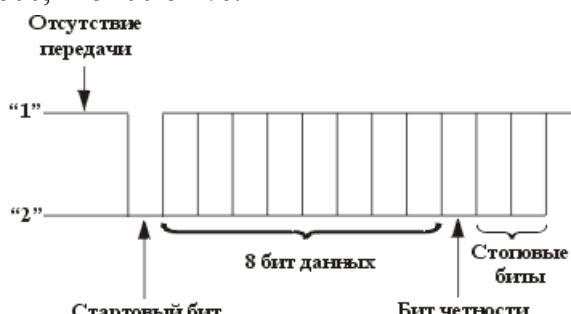

Конвейеризация (См. часть 1.) в общем случае основана на разделении подлежащей исполнению функции на более мелкие части, называемые ступенями, и выделении для каждой из них отдельного блока аппаратуры (см. рис.1.5.). Количество блоков может быть различным, например их может быть 5. Команда по тактам в процессе выполнения продвигается по блокам. Одновременно вслед за командой (раньше нее) по этим же блокам продвигаются другие команды. В результате, если каждый этап команды выполняется отдельным блоком за один такт, то на выходе процессора каждый такт, появляется результат очередной команды. Производительность при этом возрастает благодаря тому, что одновременно на различных ступенях конвейера выполняются несколько команд. Конвейерная обработка такого рода широко применяется во всех современных быстродействующих процессорах.

Рис.1.5. Разбиение процессора на блоки выполнения команд.

#### **Конвейеризация - способ обеспечения параллельности выполнения команд.**

**Суперконвейер.** Если обычный конвейер разбить на более мелкие этапы, то получим длинный или супер-конвейер. Суперконвейер позволяет поднять тактовые частоты процессора, но при этом действует ряд ограничений на длину конвейера. В данной части будут рассмотрены основные ограничения, прежде всего связанные с зависимостями между командами, которые в ряде случаев тормозят прохождение команд по конвейеру.

Для иллюстрации основных принципов построения процессоров мы будем использовать простейшую архитектуру, содержащую 32 целочисленных регистра общего назначения (R0,...,R31), 32 регистра плавающей точки (F0,...,F31) и счетчик команд PC. Будем считать, что набор команд нашего процессора включает типичные арифметические и логические операции, операции с плавающей точкой, операции пересылки данных, операции управления потоком команд и системные операции. В арифметических командах используется трехадресный формат, типичный для RISC-процессоров, а для обращения к памяти используются операции загрузки и записи содержимого регистров в память.

Выполнение типичной команды можно разделить на следующие этапы:

- выборка команды - IF (по адресу, заданному счетчиком команд, из памяти извлекается команда);

- декодирование команды / выборка operandов из регистров - ID;

- выполнение операции / вычисление эффективного адреса памяти - EX;

- обращение к памяти - MEM;

- запоминание результата - WB.

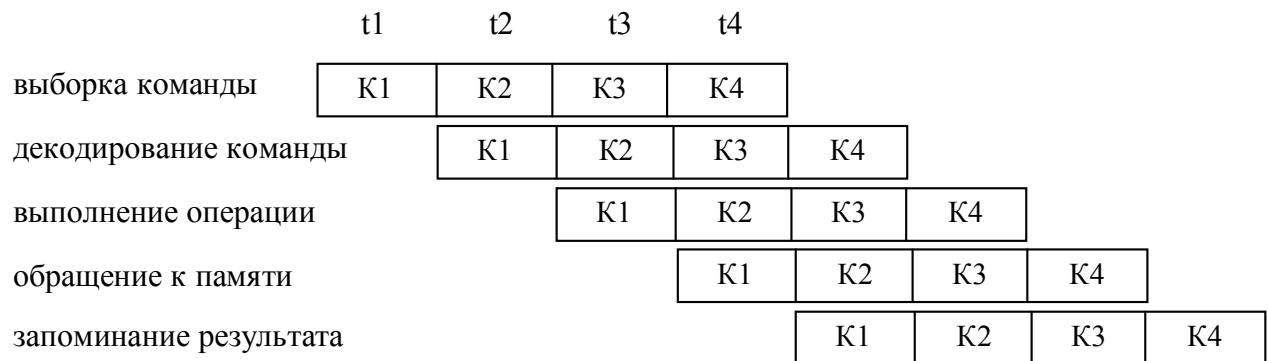

В зависимости от типа команды, вида способа адресации время выполнения команды сильно варьируется. Дольше всего выполняются этапы, связанные с обращением к памяти. Работа конвейера представлена на диаграмме, на которой изображены выполняемые команды, номера тактов и этапы выполнения команд.

Конвейеризация увеличивает пропускную способность процессора (количество команд, завершающихся в единицу времени), но она не сокращает время выполнения отдельной команды. Имеются некоторые накладные расходы на конвейеризацию, возникающие в результате несбалансированности задержки на каждой его ступени. Частота синхронизации (такт синхронизации) не может быть выше, чем время, необходимое для работы наиболее медленной ступени конвейера.

**Поток команд** - естественная последовательность команд, проходящая по конвейеру процессора. Процессор может поддерживать несколько потоков команд (суперпроцессоры 5 и 6 поколения), если для каждого потока и каждого этапа есть исполнительные элементы.

Конвейеризация эффективна только тогда, когда загрузка конвейера близка к полной, а скорость подачи новых команд и операндов соответствует максимальной производительности конвейера (характерно для RISC-процессоров). Если произойдет задержка, то параллельно будет выполняться меньше операций и суммарная производительность снизится. Такие задержки могут возникать в результате возникновения конфликтных ситуаций. Рассмотрим различные типы конфликтов, возникающие при выполнении команд в конвейере, и способы их разрешения.

Существуют три класса конфликтов:

1. Структурные конфликты, которые возникают из-за конфликтов по ресурсам, когда аппаратные средства не могут поддерживать все возможные комбинации команд в режиме одновременного выполнения с совмещением.

2. Конфликты по данным, возникающие в случае, когда выполнение одной команды зависит от результата выполнения предыдущей команды.

3. Конфликты по управлению, которые возникают при конвейеризации команд переходов и других команд, которые изменяют значение счетчика команд.

Конфликты в конвейере приводят к необходимости приостановки выполнения команд (pipeline stall). Обычно в простейших конвейерах, если приостанавливается какая-либо команда, то все следующие за ней команды также приостанавливаются. Команды, предшествующие приостановленной, могут продолжать выполняться, но во время приостановки не выбирается ни одна новая команда. Среднее количество тактов выполнения команды из-за конфликтов увеличивается по сравнению с идеальным конвейером.

|                                                                 |                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Среднее количество тактов выполнения команды в конвейере</b> | <b><math>CPI \text{ конвейера} = CPI \text{ идеального конвейера} +</math></b><br>+ Приостановки из-за структурных конфликтов +<br>+ Приостановки из-за конфликтов по данным +<br>+ Приостановки из-за конфликтов по управлению |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

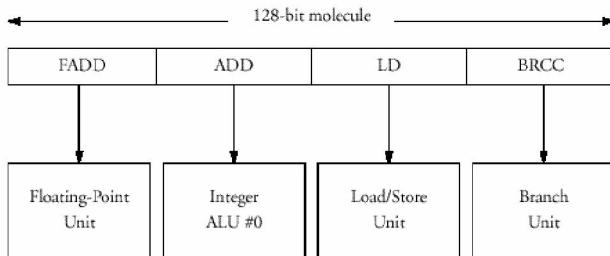

### **Суперскалярная архитектура. Процессоры с длинным командным словом.**

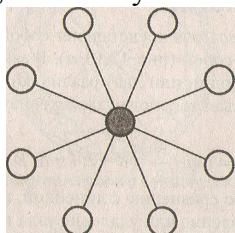

Иерархия параллельной обработки данных включает четыре уровня параллельности, каждый из которых должен быть поддержан аппаратурой.

1. Слабо связанные задачи общего проекта - решаются на своих процессорах (процессорная сеть).

2. Отдельные ветви или потоки программ, которые выполняются параллельно (мультискалярный процессор, многоядерный процессор или мультипроцессорная система).

3. Одновременное выполнение нескольких команд (суперскалярный процессор, процессоры с длинным командным словом.).

4. Разбиение процесса выполнения команд на части, которые можно выполнять параллельно (конвейерный процессор).

Обеспечение параллельности на первых двух уровнях определяется не только аппаратурой, а в первую очередь решаемыми задачами и алгоритмами разбиения этих задач на параллельные потоки. Вторые два уровня - параллельность уровня команд. На этих уровнях параллельное выполнение команд напрямую не зависит от выполняемых программ. Обеспечение параллельности уровня команд является основным средством достижения высокого быстродействия микропроцессора.

Есть два крайних подхода, при возможных промежуточных, к отображению присущего микропроцессору внутреннего параллелизма обработки данных на архитектурном уровне в системе команд. Первый подход более консервативен и состоит в том, что никакого указания на параллельную обработку внутри процессора система команд не содержит. Такие процессоры относятся к классу суперскалярных. Термин суперскалярный появился в 1987 году. Во втором подходе в формате команд уже заложена параллельной. В специально отведенных полях команды каждому из параллельно работающих обрабатывающих устройств предписывается действие, которое устройство должно совершить. Такие процессоры называются процессорами с длинным командным словом (VLIW). Предполагается, что существуют компиляторы с языков высокого уровня, которые готовят программы для загрузки их в VLIW-микропроцессоры или уже на низком уровне языка Ассемблера формируются длинные команды. В мультискалярных процессорах реализуется третий подход, связанный с обеспечением параллельности выполнения команд. Мультискалярный микропроцессор содержит несколько процессорных элементов со своими счетчиками команд, которые выполняют свои ветви программ. Такой микропроцессор представляет собой однокристальную многопроцессорную систему с разделяемой памятью и работающей на 2 уровне параллельности.

|                                              |                                                                           |                                                       |

|----------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------|

| Суперскалярность только на уровне аппаратуры | Процессоры с длинным командным словом (very long instruction word - VLIW) | Мультискалярные процессоры<br>Многоядерные процессоры |

| Параллельность уровня команды.               |                                                                           |                                                       |

Суперскалярность состоит в способности независимо выполнять команды параллельно на разных конвейерах. Очередная команда в такой структуре поступает на первый освободившийся конвейер (если конвейеры одинаковы). В реализациях структура, как правило, более сложная (см. напр. Pentium Pro), когда невозможно выделить отдельные “нити” нескольких конвейеров, но, тем не менее, для каждой стадии выполнения команды существует более одного исполнительного блока.

Основная идея, определяющая развитие суперскалярных микропроцессоров, заключается в построении возможно большего количества параллельных структур при сохранении традиционных последовательных программ. Это означает, что компиляторы и аппаратура микропроцессора сами, без вмешательства программиста, обеспечивают загрузку параллельно работающих функциональных устройств микропроцессора.

Текст последовательной программы, представленной на языке высокого уровня, компилируется в машинный код, отражающий **статическую структуру программы**, т.е. упорядоченное множество команд в памяти компьютера. Процесс выполнения программы с конкретными наборами входных данных может быть представлен **динамической структурой программы**, т.е. множеством последовательностей инструкций в порядке их исполнения.

Повысить степень параллелизма программы можно, изменения соответствующим образом ее статическую или динамическую структуру. Поскольку статическая структура программы однозначно соответствует ее исходному тексту, то изменение статической структуры сводится к изменению исходного кода, что, в общем случае, не всегда возможно. Динамическая же структура программы может быть изменена при неизменной статической структуре. Целью такого изменения является повышение степени параллельности исполнения команд.

При описании архитектур суперскалярных процессоров часто используется модель **окна исполнения**. При исполнении программы микропроцессор как бы продвигает по статической структуре программы окно исполнения. Команды в окне могут исполняться параллельно, если между ними нет зависимости.

Динамическая последовательность команд структурирована (разделена) зависимостями по данным и управлению. Зависимости по управлению (которые проявляются как переходы по условию) представляют главное препятствие высокопараллельному выполнению потому, что эти зависимости должны быть установлены прежде чем будут выполнены все последующие команды.

## **1.4. Структурные конфликты, зависимости по данным и по управлению**

### **1.4.1. Структурные конфликты**

Совмещенный режим выполнения команд в общем случае требует конвейеризации функциональных устройств и дублирования ресурсов для разрешения всех возможных комбинаций команд в конвейере. Если какая-нибудь комбинация команд не может быть принята из-за конфликта по ресурсам, то говорят, что в машине имеется структурный конфликт. Наиболее типичным примером машин, в которых возможно появление структурных конфликтов, являются машины с не полностью конвейерными функциональными устройствами. Время работы такого устройства может составлять несколько тактов синхронизации конвейера. В этом случае последовательные команды, которые используют данное функциональное устройство,

не могут поступать в него в каждом такте. Другая возможность появления структурных конфликтов связана с недостаточным дублированием некоторых ресурсов, что препятствует выполнению произвольной последовательности команд в конвейере без его приостановки. Например, машина может иметь только один порт записи в регистровый файл, но при определенных обстоятельствах конвейеру может потребоваться выполнить две записи в регистровый файл в одном такте. Это также приведет к структурному конфликту.

#### Структурные зависимости – конфликт из-за недостаточности ресурсов.

Структурные конфликты возникают, например, и в машинах, в которых имеется единственный конвейер памяти для команд и данных. В этом случае, когда одна команда содержит обращение к памяти за данными, оно будет конфликтовать с выборкой более поздней команды из памяти. Чтобы разрешить эту ситуацию, можно просто приостановить конвейер на один такт, когда происходит обращение к памяти за данными. Подобная приостановка часто называется "конвейерным пузырем" (pipeline bubble) или просто пузырем, поскольку пузырь проходит по конвейеру, занимая место, но не выполняя никакой полезной работы. Пример структурного конфликта при реализации памяти с одним портом представлен на рис. 7.6.

Возникает вопрос: почему разработчики допускают наличие структурных конфликтов? Для этого имеются две причины: снижение стоимости и уменьшение задержки устройства. Конвейеризация всех функциональных устройств может оказаться слишком дорогой. Машины, допускающие два обращения к памяти в одном такте, должны иметь удвоенную пропускную способность памяти, например, путем организации раздельных кэшей для команд и данных.

| Команда   | Номер такта |    |    |       |     |     |    |     |     |

|-----------|-------------|----|----|-------|-----|-----|----|-----|-----|

|           | 1           | 2  | 3  | 4     | 5   | 6   | 7  | 8   | 9   |

| Команда 1 | IF          | ID | EX | MEM   | WB  |     |    |     |     |

| Команда 2 |             | IF | ID | EX    | MEM | WB  |    |     |     |

| Команда 3 |             |    | IF | ID    | EX  | MEM | WB |     |     |

| Команда 4 |             |    |    | stall | IF  | ID  | EX | MEM | WB  |

| Команда 5 |             |    |    |       |     | IF  | ID | EX  | MEM |

| Команда 6 |             |    |    |       |     |     | IF | ID  | EX  |

Рис. 1.6. Диаграмма работы конвейера при структурном конфликте

#### 1.4.2. Конфликты по данным и методы их преодоления

Зависимости по данным обусловлены использованием одних и тех же ресурсов памяти (регистров, ячеек памяти) в разных командах. Рассмотрим конвейерное выполнение последовательности команд на рисунке 7.7.

|                |    |    |    |     |     |     |     |     |

|----------------|----|----|----|-----|-----|-----|-----|-----|

| ADD R1,R2,R3   | IF | ID | EX | MEM | WB  |     |     |     |

| SUB R4,R1,R5   |    | IF | ID | EX  | MEM | WB  |     |     |

| AND R6,R1,R7   |    |    | IF | ID  | EX  | MEM | WB  |     |

| OR R8,R1,R9    |    |    |    | IF  | ID  | EX  | MEM | WB  |

| XOR R10,R1,R11 |    |    |    |     | IF  | ID  | EX  | MEM |

Рис. 1.7. Последовательность команд в конвейере

В этом примере все команды, следующие за командой ADD, используют результат ее выполнения. Команда ADD записывает результат в регистр R1, а команда SUB читает это значение. Если не предпринять никаких мер для того, чтобы предотвратить этот конфликт, команда SUB прочитает неправильное значение и попытается его использовать. На самом деле значение, используемое командой SUB,

является даже неопределенным: хотя логично предположить, что SUB всегда будет использовать значение R1, которое было присвоено какой-либо командой, предшествовавшей ADD, это не всегда так. Если произойдет прерывание между командами ADD и SUB, то команда ADD завершится, и значение R1 в этой точке будет соответствовать результату ADD.

Проблема может быть разрешена с помощью достаточно простой аппаратной техники, которая называется обходом (data bypassing), иногда закороткой (short-circuiting). Результат операции АЛУ с его выходного регистра всегда снова подается назад на входы АЛУ. Если аппаратура обнаруживает, что предыдущая операция АЛУ записывает результат в регистр, соответствующий источнику операнда для следующей операции АЛУ, то логические схемы управления выбирают в качестве входа для АЛУ результат, поступающий по цепи "обхода", а не значение, прочитанное из регистрового файла.

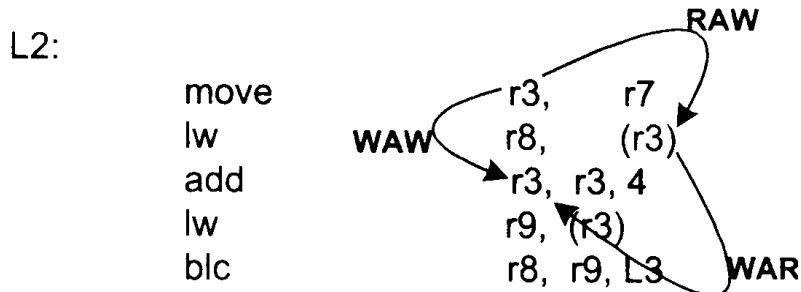

Классификация всех видов зависимостей представлена в таблице и на рис. 7.8.

| RAR - "чтение после чтения" | WAR - "запись после чтения" | WAW - "запись после записи" | RAW - "чтение после записи" |

|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Отсутствие зависимостей     | Лишние зависимости          |                             | Действительная зависимость  |

Рис.1.8. Зависимости по данным

Возможны три конфликта по данным в зависимости от порядка операций чтения и записи (Рассмотрим две команды  $i$  и  $j$ , при этом  $i$  предшествует  $j$ ):

- RAW (чтение после записи) -  $j$  пытается прочитать операнд-источник данных прежде, чем  $i$  туда запишет. Таким образом,  $j$  может некорректно получить старое значение. Это наиболее общий тип конфликтов, способ их преодоления с помощью механизма "обходов" рассмотрен ранее.

- WAR (запись после чтения) -  $j$  пытается записать результат в приемник прежде, чем он считывается оттуда командой  $i$ , так что  $i$  может некорректно получить новое значение. Особенно часто конфликты такого рода могут возникать в системах, допускающих выполнение команд не в порядке их расположения в программном коде (6 поколение процессоров).

- WAW (запись после записи) -  $j$  пытается записать операнд прежде, чем будет записан результат команды  $i$ , т.е. записи заканчиваются в неверном порядке, оставляя в приемнике значение, записанное командой  $i$ , а не  $j$ . Этот тип конфликтов присутствует только в конвейерах, которые выполняют запись со многих ступеней.

К сожалению не все потенциальные конфликты по данным могут обрабатываться с помощью механизма "обходов". Рассмотрим следующую последовательность команд (рис.7.9):

|              |    |    |    |       |    |     |     |     |

|--------------|----|----|----|-------|----|-----|-----|-----|

| LW R1,32(R6) | IF | ID | EX | MEM   | WB |     |     |     |

| ADD R4,R1,R7 |    | IF | ID | stall | EX | MEM | WB  |     |

| SUB R5,R1,R8 |    |    | IF | stall | ID | EX  | MEM | WB  |

| AND R6,R1,R7 |    |    |    | stall | IF | ID  | EX  | MEM |

Рис. 1.9. Последовательность команд в конвейере

Этот случай отличается от последовательности подряд идущих команд АЛУ. Команда загрузки (LW) регистра R1 из памяти имеет задержку, которая не может быть устранена обычной "пересылкой". Вместо этого нам нужна дополнительная аппаратура, называемая аппаратурой внутренних блокировок конвейера (pipeline interlock). Эта аппаратура приостанавливает конвейер начиная с команды, которая хочет использовать данные в то время, когда предыдущая команда, результат которой является операндом для нашей, вырабатывает этот результат. Эта аппаратура вызывает приостановку конвейера или появление "пузыря" точно также, как и в случае структурных конфликтов.

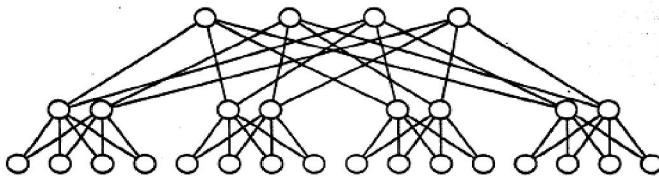

Многие современные компиляторы используют технику планирования команд для улучшения производительности конвейера. В простейшем алгоритме компилятор просто планирует распределение команд в одном и том же базовом блоке. **Базовый блок** представляет собой линейный участок последовательности программного кода, в котором отсутствуют команды перехода, за исключением начала и конца участка (переходы внутрь этого участка тоже должны отсутствовать). Планирование такой последовательности команд осуществляется достаточно просто, поскольку компилятор знает, что каждая команда в блоке будет выполняться, если выполняется первая из них, и можно просто построить граф зависимостей этих команд и упорядочить их так, чтобы минимизировать приостановки конвейера.

Однако, требуются более сложные алгоритмы планирования. Они базируются на следующих методах.

**1. Методы динамической оптимизации** ("out-of-order execution" - неупорядоченное выполнение).

Основными средствами динамической оптимизации являются:

Размещение схемы обнаружения конфликтов в возможно более низкой точке конвейера команд.

Буферизация команд, ожидающих разрешения конфликта, и выдача последующих, логически не связанных команд, в "обход" буфера. В этом случае команды могут выдаваться на выполнение не в том порядке, в котором они расположены в программе.

Соответствующая организация коммутирующих магистралей, обеспечивающая засылку результата операции непосредственно в буфер, хранящий логически зависимую команду, задержанную из-за конфликта, или непосредственно на вход функционального устройства до того, как этот результат будет записан в регистровый файл или в память.

**2. Метод переименования регистров (register renaming).**

Выделяются **логические регистры**, обращение к которым выполняется с помощью соответствующих полей команды, и **физические регистры**, которые размещаются в аппаратном регистровом файле процессора. Номера логических регистров динамически отображаются на номера физических регистров посредством таблиц отображения, которые обновляются после декодирования каждой команды. Каждый новый результат записывается в новый физический регистр. Однако предыдущее значение каждого логического регистра сохраняется и может быть

восстановлено в случае, если выполнение команды должно быть прервано из-за возникновения исключительной ситуации или неправильного предсказания направления условного перехода.

В процессе выполнения программы генерируется множество временных регистровых результатов. Эти временные значения записываются в регистровые файлы вместе с постоянными значениями. Временное значение становится новым постоянным значением, когда завершается выполнение команды (фиксируется ее результат). В свою очередь, завершение выполнения команды происходит, когда все предыдущие команды успешно завершились в заданном программой порядке.

Программист имеет дело только с логическими регистрами. Реализация физических регистров от него скрыта. Метод переименования регистров упрощает контроль зависимостей по данным.

### **1.4.3. Конфликты по управлению**

Существует две разновидности переходов: безусловные, всегда передающие управление по новому указанному адресу, и условные, которые меняют или не меняют ход выполнения программы в зависимости от результата сравнения или выполнения какого-либо другого условия. (Когда условный переход не выполняется, программа просто продолжает выполнение следующей по порядку команды.)

В типичной программе до 10% команд могут быть безусловными переходами, и еще 10-20% - представлять собой условные переходы. Безусловные переходы проблем не вызывают; процессор "уверен", что они будут выполнены и поэтому просто начинает выборку команд по указанному адресу. Команды условных переходов представляют гораздо большие трудности, потому что процессор не может "знать", будет ли переход выполнен или нет до тех пор, пока команда не пройдет исполнительную ступень конвейера.

Однако ожидание, пока команда ветвления покинет исполнительную ступень, означает отказ от возможности выборки и обработки многих команд. Процессору нужен некий алгоритм, который позволит ему "угадать", будет ли выполняться переход или нет. Если предсказание окажется верным, то выполнение продолжится с малой задержкой либо вовсе без нее. Если же предположение ошибочно, то частично выполненные команды придется удалить из конвейера, а новые команды выбрать из области памяти с правильным адресом, декодировать и выполнить их. Это повлечет за собой существенное снижение производительности - особенно ощутимое в процессорах, которые, как Р6, имеют многочисленные и глубокие конвейеры. Если Р6 ошибается в предсказании перехода, он может потерять от 4 до 15 тактов.

Конфликты по управлению могут вызывать даже большие потери производительности конвейера, чем конфликты по данным. Когда выполняется команда условного перехода, она может либо изменить, либо не изменить значение счетчика команд. Если команда условного перехода заменяет счетчик команд значением адреса, вычисленного в команде, то переход называется выполняемым; в противном случае, он называется невыполняемым.

Простейший метод работы с условными переходами заключается в приостановке конвейера, как только обнаружена команда условного перехода до тех пор, пока она не достигнет ступени конвейера, которая вычисляет новое значение счетчика команд. Такие приостановки конвейера из-за конфликтов по управлению встречаются часто и должны реализовываться иначе, чем приостановки из-за конфликтов по данным, поскольку выборка команды, следующей за командой условного перехода, должна

быть выполнена как можно быстрее, как только мы узнаем окончательное направление команды условного перехода.

| Команда перехода  | IF | ID | EX    | MEM   | WB    |       |       |       |       |     |

|-------------------|----|----|-------|-------|-------|-------|-------|-------|-------|-----|

| Следующая команда |    | IF | stall | stall | ID    | EX    | MEM   | WB    |       |     |

| Следующая ком. +1 |    |    | stall | stall | stall | IF    | ID    | EX    | MEM   | WB  |

| Следующая ком. +2 |    |    |       | stall | stall | stall | IF    | ID    | EX    | MEM |

| Следующая ком. +3 |    |    |       |       | stall | stall | stall | IF    | ID    | EX  |

| Следующая ком. +4 |    |    |       |       |       | stall | stall | stall | IF    | ID  |

| Следующая ком. +5 |    |    |       |       |       |       | stall | stall | stall | IF  |

Рис. 1.10. Последовательность команд в конвейере

Если конвейер будет приостановлен на три такта на каждой команде условного перехода, то это может существенно отразиться на производительности машины. При частоте команд условного перехода в программах, равной 30% и идеальном CPI машина с приостановками условных переходов достигает примерно только половины ускорения, получаемого за счет конвейерной организации. Число тактов, теряемых при приостановках из-за условных переходов, может быть уменьшено на каждом этапе выполнения команды следующими способами: раннее распознание команды условного ветвления, проверка и предсказание выполнения условия перехода, ускоренное (раннее) вычисление целевого адреса перехода, быстрая передача управления, в случае перехода. Подробное рассмотрение методов повышения производительности будет проведено ниже при анализе архитектуру процессоров.

Имеется несколько простых методов сокращения приостановок конвейера, возникающих из-за задержек выполнения условных переходов:

#### **Метод выжидания**

Простейшая схема обработки команд условного перехода заключается в замораживании или подавлении операций в конвейере, путем блокировки выполнения любой команды, следующей за командой условного перехода, до тех пор, пока не станет известным направление перехода. Рис. 7.10 отражал именно такой подход.

#### **Метод возврата**

Более хорошая и не на много более сложная схема состоит в том, чтобы прогнозировать условный переход как невыполнимый. При этом аппаратура должна просто продолжать выполнение программы, как если бы условный переход вовсе не выполнялся. В этом случае необходимо позаботиться о том, чтобы не изменить состояние машины до тех пор, пока направление перехода не станет окончательно известным. В некоторых машинах эта схема с невыполнимыми по прогнозу условными переходами реализована путем продолжения выборки команд, как если бы условный переход был обычной командой. Поведение конвейера выглядит так, как будто ничего необычного не происходит. Однако, если условный переход на самом деле выполняется, то необходимо очистить конвейер от команд, выбранных вслед за командой условного перехода и заново повторить выборку команд.

#### **Задержанные переходы**

В задержанном переходе команда перехода выполняется с задержкой на несколько тактов, которые используются для выполнения других команд. Эти команды находятся в слотах (временных интервалах) задержанного перехода. Задача программного обеспечения заключается в том, чтобы сделать команды, следующие за командой перехода, действительными и полезными. Аппаратура гарантирует реальное выполнение этих команд перед выполнением собственно перехода. Представим два из приемов оптимизации:

1. Слот задержки заполняется независимой командой, находящейся перед командой условного перехода.

2. Слот задержки заполняется командой, находящейся по целевому адресу команды перехода. Стратегии (2) отдаётся предпочтение, когда с высокой вероятностью переход является выполняемым, например, если это переход на начало цикла.

Таким образом, даже для простых алгоритмов планирования требуется предсказывать переходы. Кроме простых методов преодоления зависимостей по управлению, современные процессоры используют сложные методы, то есть такие, которые требуют большего количества аппаратуры для их реализации. Перечислим, а затем и рассмотрим, основные методы:

- Раннее распознание команды условного ветвления

- Проверка и предсказание выполнения условия перехода

- Ускоренное (раннее) вычисление целевого адреса перехода

- Быстрая передача управления, в случае перехода

- Свертывание переходов

- Параллельное выполнение команд из окна исполнения

- Разворачивание циклов

#### **1.4.4. Проблемы реализации точного прерывания в конвейере**

Обработка прерываний в конвейерной машине оказывается более сложной из-за того, что совмещенное выполнение команд затрудняет определение возможности безопасного изменения состояния машины произвольной командой. В конвейерной машине команда выполняется по этапам, и ее завершение осуществляется через несколько тактов после выдачи для выполнения. Еще в процессе выполнения отдельных этапов команда может изменить состояние машины. Тем временем возникшее прерывание может вынудить машину прервать выполнение еще не завершенных команд.

Например, для нашего простейшего конвейера прерывание по отсутствию страницы виртуальной памяти при выборке данных не может произойти до этапа выборки из памяти (MEM). В момент возникновения этого прерывания в процессе обработки уже будут находиться несколько команд. Поскольку подобное прерывание должно обеспечить возврат для продолжения программы и требует переключения на другой процесс (операционную систему), необходимо надежно очистить конвейер и сохранить состояние машины таким, чтобы повторное выполнение команды после возврата из прерывания осуществлялось при корректном состоянии машины. Обычно это реализуется путем сохранения адреса команды (PC), вызвавшей прерывание.

Когда происходит прерывание, для корректного сохранения состояния машины необходимо выполнить следующие шаги:

1. В последовательность команд, поступающих на обработку в конвейер, принудительно вставить команду перехода на прерывание.

2. Пока выполняется команда перехода на прерывание, погасить все требования записи, выставленные командой, вызвавшей прерывание, а также всеми следующими за ней в конвейере командами.

3. После передачи управления подпрограмме обработки прерываний операционной системы, она немедленно должна сохранить значение адреса команды (PC), вызвавшей прерывание. Это значение будет использоваться позже для организации возврата из прерывания.

Другая проблема, связанная с реализацией команд с большим временем выполнения, может быть проиллюстрирована с помощью следующей последовательности команд:

```

DIVF F0,F2,F4

ADDF F10,F10,F8

SUBF F12,F12,F14

```

Эта последовательность команд выглядит очень просто. В ней отсутствуют какие-либо зависимости. Однако она приводит к появлению новых проблем из-за того, что выданная раньше команда может завершиться после команды, выданной для выполнения позже. В данном примере можно ожидать, что команды ADDF и SUBF завершаться раньше, чем завершится команда DIVF. Этот эффект является типичным для конвейеров команд с большим временем выполнения и называется внеочередным завершением команд (out-of-order completion). Тогда, например, если команда DIVF вызовет арифметическое прерывание после завершения команды ADDF, мы не сможем реализовать точное прерывание на уровне аппаратуры. В действительности, поскольку команда ADDF меняет значение одного из своих операндов, невозможно даже с помощью программных средств восстановить состояние, которое было перед выполнением команды DIVF.

Имеются четыре возможных подхода для работы в условиях внеочередного завершения команд.

Первый из них просто игнорирует проблему и предлагает механизмы неточного прерывания.

Второй подход заключается в буферизации результатов операции до момента завершения выполнения всех команд, предшествовавших данной. В некоторых машинах используется этот подход, но он становится все более дорогостоящим, если отличия во времени выполнения разных команд велики, поскольку становится большим количество результатов, которые необходимо буферизовать.

Третий используемый метод заключается в том, чтобы разрешить в ряде случаев неточные прерывания, но при этом сохранить достаточно информации, чтобы подпрограмма обработки прерывания могла выполнить точную последовательность прерывания. Это предполагает наличие информации о находившихся в конвейере командах и их адресов. Тогда после обработки прерывания, программное обеспечение завершает выполнение всех команд, предшествовавших последней завершившейся команде, а затем последовательность может быть запущена заново.

Четвертый метод представляет собой гибридную схему, которая позволяет продолжать выдачу команд только если известно, что все команды, предшествовавшие выдаваемой, будут завершены без прерывания. Это гарантирует, что в случае возникновения прерывания ни одна следующая за ней команда не будет завершена, а все предшествующие будут завершены. Иногда это означает необходимость приостановки машины для поддержки точных прерываний.

#### **1.4.5. Статическое и динамическое предсказание переходов**

Существуют два основных метода предсказаний переходов - статический (static) и динамический (dynamic). Статические методы предсказания ветвлений слишком упрощены; они предписывают всегда выполнять или не выполнять определенные типы переходов. В некоторых процессорах (не принадлежащих к семейству x86) команды содержат "намек" на направление предполагаемого перехода, который компилятор может сделать на основе ожидаемого им поведения программы. Но в целом более эффективное решение - динамический алгоритм предсказания ветвлений, который на

самом деле оценивает поведение команд перехода за предшествующий период времени (поскольку один и тот же переход часто выполняется более чем один раз, например, в цикле). Благодаря информации о предыстории предсказания будущих ветвлений могут делаться гораздо более точно.

### **Методы статического предсказания**

Методы статического предсказания используются на этапе выполнения команды и на этапе работы компилятора. На этапе выполнения команды определяются коды операций, которые чаще дают ветвление. На этапе работы компилятора используют два основных метода: метод исследования структуры программы и метод использования информации о профиле выполнения программы, который собран в результате предварительных запусков программы (трассировка программы). Компилятор устанавливает флаг, указывающий на направление перехода.

Использование структуры программы достаточно просто: в качестве исходной точки можно предположить, например, что все идущие назад по программе переходы являются выполняемыми, а идущие вперед по программе - невыполнимыми. Однако эта схема не очень эффективна для большинства программ. Основываясь только на структуре программы просто трудно сделать лучший прогноз.

Альтернативная техника для предсказания переходов основана на информации о профиле выполнения программы, собранной во время предыдущих прогонов. Ключевым моментом, который делает этот подход заслуживающим внимания, является то, что поведение переходов при выполнении программы часто повторяется, т.е. каждый отдельный переход в программе часто оказывается смещенным в одну из сторон: он либо выполняемый, либо невыполнимый. Проведенные многими авторами исследования показывают достаточно успешное предсказания переходов с использованием этой стратегии.

### **Методы динамического предсказания**

Методы динамического предсказания основаны на использовании информации об истории выполнения данного ветвления.

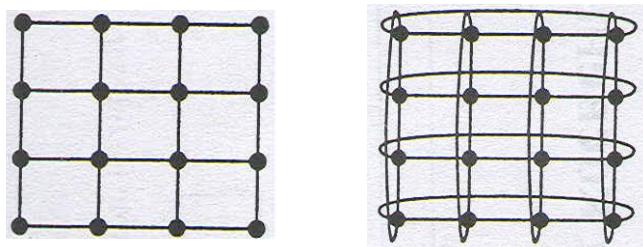

#### 1. Прогнозирование перехода.

Простейшей схемой динамического прогнозирования направления условных переходов является **буфер прогнозирования условных переходов** (branch-prediction buffer) или **таблица "истории" условных переходов** (branch history table). Буфер прогнозирования условных переходов представляет собой небольшую память, адресуемую с помощью младших разрядов адреса команды перехода. Каждая ячейка этой памяти содержит один бит, который говорит о том, был ли предыдущий переход выполняемым или нет. Это простейший вид такого рода буфера. Прогноз - это только предположение, которое рассматривается как корректное, и выборка команд начинается по прогнозируемому направлению. Если же предположение окажется неверным, бит прогноза инвертируется. Конечно, такой буфер можно рассматривать как кэш-память, каждое обращение, к которой является попаданием, и производительность буфера зависит от того, насколько часто прогноз применялся и насколько он оказался точным.

Таблица предсказания перехода

| Бит<br>Достоверн. | Адрес команды<br>перехода (тег) | Биты<br>Перехода/<br>Прогноза |  |

|-------------------|---------------------------------|-------------------------------|--|

|                   |                                 |                               |  |

|                   |                                 |                               |  |

|                   |                                 |                               |  |

Рис. 1.11. Схема таблицы перехода

Простая **однобитовая схема** прогноза имеет недостаточную производительность.

Рассмотрим, например, команду условного перехода в цикле, которая являлась выполняемым переходом последовательно девять раз подряд, а затем однажды невыполняемым. Направление перехода будет неправильно предсказываться при первой и при последней итерации цикла. Неправильный прогноз последней итерации цикла неизбежен, поскольку бит прогноза будет говорить, что переход "выполнимый" (переход был девять раз подряд выполняемым). Неправильный прогноз на первой итерации происходит из-за того, что бит прогноза инвертируется при предыдущем выполнении последней итерации цикла, поскольку в этой итерации переход был невыполняемым. Таким образом, точность прогноза для перехода, который выполнялся в 90% случаев, составила только 80% (2 некорректных прогноза и 8 корректных). В общем случае, для команд условного перехода, используемых для организации циклов, переход является выполняемым много раз подряд, а затем один раз оказывается невыполняемым. Поэтому однобитовая схема прогнозирования будет неправильно предсказывать направление перехода дважды (при первой и при последней итерации).

Рис. 1.12. Двухбитный конечный автомат для прогнозирования переходов.

Для исправления этого положения часто используется **схема двухбитового прогноза**. В двухбитовой схеме прогноз должен быть сделан неверно дважды, прежде чем он изменится на противоположное значение.

Этот алгоритм можно представить в виде конечного автомата с четырьмя состояниями (рис.). После ряда последовательных успешных предсказаний "перехода нет" конечный автомат будет находиться в состоянии 00 и в следующий раз также прогнозировать, что "перехода нет". Если этот прогноз неправильный, автомат переходит в состояние 01, но в следующий раз все равно предсказывает отсутствие перехода. Только в том случае, если это последнее предсказание ошибочно, конечный автомат перейдет в состояние 11 и будет все время прогнозировать наличие перехода. Фактически, левый бит - это прогноз, а правый бит - это то, что было сделано в прошлый раз (то есть был ли совершен переход).

Двухбитовая схема прогнозирования в действительности является частным случаем более общей схемы, которая в каждой строке буфера прогнозирования имеет  $n$ -битовый счетчик.

Этот счетчик может принимать значения от 0 до  $2^n - 1$ . Тогда схема прогноза будет следующей:

- Если значение счетчика больше или равно  $2^{n-1}$  (точка на середине интервала), то переход прогнозируется как выполняемый. Если направление перехода предсказано правильно, к значению счетчика добавляется единица (если только оно не достигло максимальной величины); если прогноз был неверным, из значения счетчика вычитается единица.

- Если значение счетчика меньше, чем  $2^{n-1}$ , то переход прогнозируется как невыполняемый. Если направление перехода предсказано правильно, из значения счетчика вычитается единица (если только не достигнуто значение 0); если прогноз был неверным, к значению счетчика добавляется единица.

Исследования  $n$ -битовых схем прогнозирования показали, что двухбитовая схема работает почти также хорошо, и поэтому в большинстве систем применяются двухбитовые схемы прогноза, а не  $n$ -битовые.

Буфер прогнозирования переходов может быть реализован в виде небольшой специальной кэш-памяти, доступ к которой осуществляется с помощью адреса команды во время стадии выборки команды в конвейере (IF), или как пара битов, связанных с каждым блоком кэш-памяти команд и выбираемых с каждой командой (например, в процессоре Alpha21164). Если команда декодируется как команда перехода, и если переход спрогнозирован как выполняемый, выборка команд начинается с целевого адреса, как только станет известным новое значение счетчика команд. В противном случае продолжается последовательная выборка и выполнение команд. Если прогноз оказался неверным, значение битов прогноза меняется.

Какую точность можно ожидать от буфера прогнозирования переходов на реальных приложениях при использовании 2 бит на каждую строку буфера? Для набора оценочных тестов SPEC-89 буфер прогнозирования переходов с 4096 строками дает точность прогноза от 99% до 82%. Следует отметить, что буфер емкостью 4К строк считается очень большим. Буфера меньшего объема дадут худшие результаты.

Рассмотренные двухбитовые схемы прогнозирования используют информацию о недавнем поведении команды условного перехода для прогноза будущего поведения этой команды. Вероятно можно улучшить точность прогноза, если учитывать не только поведение того перехода, который мы пытаемся предсказать, но рассматривать также и недавнее поведение других команд перехода.

Схемы прогнозирования, которые для предсказания направления перехода используют поведение других команд перехода, называются **коррелированными или двухуровневыми схемами прогнозирования**. Схема прогнозирования называется прогнозом (1,1), если она использует поведение одного последнего перехода для выбора из пары однобитовых схем прогнозирования на каждый переход. В общем случае схема прогнозирования ( $m,n$ ) использует поведение последних  $m$  переходов для выбора из  $2^m$  схем прогнозирования, каждая из которых представляет собой  $n$ -битовую схему прогнозирования для каждого отдельного перехода. Привлекательность такого типа коррелируемых схем прогнозирования переходов заключается в том, что они могут давать больший процент успешного прогнозирования, чем обычная двухбитовая схема, и требуют очень небольшого объема дополнительной аппаратуры.

## 2. Быстрое определения адреса перехода.

Рассмотрим ситуацию, при которой на стадии выборки команд находится команда перехода (на следующей стадии будет осуществляться ее дешифрация). Тогда чтобы сократить потери, необходимо знать, по какому адресу выбирать следующую команду. Это означает, что нам как-то надо выяснить, что еще недешифрированная команда в самом деле является командой перехода, и чему равно следующее значение счетчика адресов команд. Если все это мы будем знать, то потери на команду перехода могут быть сведены к нулю. Специальный аппаратный кэш прогнозирования переходов, который хранит прогнозируемый адрес следующей команды, называется **буфером целевых адресов переходов** (branch-target buffer).

**Таблица предсказания с буфером целевых адресов переходов**

| Бит Достоверн. | Адрес команды перехода | Биты Перехода | Целевой адрес |

|----------------|------------------------|---------------|---------------|

|                |                        |               |               |

|                |                        |               |               |

|                |                        |               |               |

Рис. 1.13. Схема таблицы перехода с буфером целевых адресов.

Каждая строка этого буфера включает программный адрес команды перехода, прогнозируемый адрес следующей команды и предысторию команды перехода. Биты предыстории представляют собой информацию о выполнении или невыполнении условий перехода данной команды в прошлом. Обращение к буферу целевых адресов перехода (сравнение с полями программных адресов команд перехода) производится с помощью текущего значения счетчика команд на этапе выборки очередной команды. Если обнаружено совпадение, то по предыстории команды прогнозируется выполнение или невыполнение условий команды перехода, и немедленно производится выборка и дешифрация команд из прогнозируемой ветви программы. Считается, что предыстория перехода, содержащая информацию о двух предшествующих случаях выполнения этой команды, позволяет прогнозировать развитие событий с вполне достаточной вероятностью.

## 3. Метод свертывания переходов (branch folding)

Основной смысл метода заключается в том, чтобы хранить в процессоре одну или несколько команд из прогнозируемой ветви перехода. Этот метод может применяться как в совокупности с буфером целевых адресов перехода, так и без него, и имеет два преимущества. Во-первых, он позволяет выполнять обращения к буферу целевых адресов перехода в течение более длительного времени, а не только в течение времени последовательной выборки команд. Это позволяет реализовать буфер большего объема. Во-вторых, буферизация самих целевых команд позволяет реализовать нулевое время выполнения самих команд безусловного перехода, а в некоторых случаях и нулевое время выполнения условных переходов.

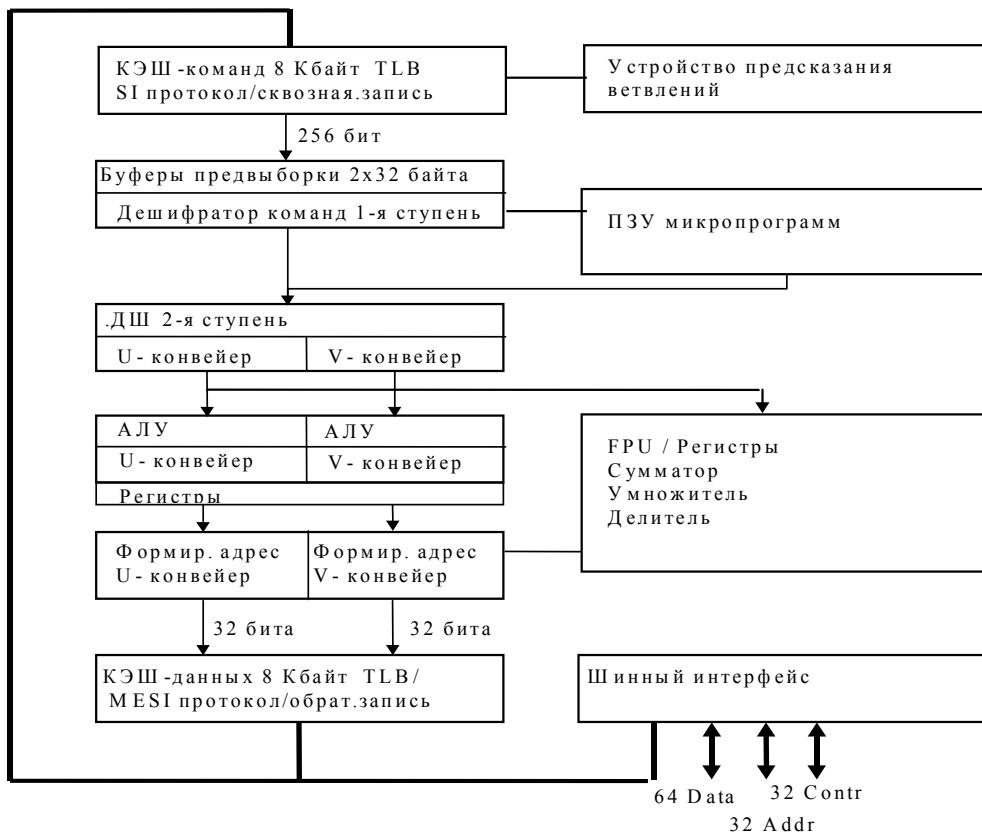

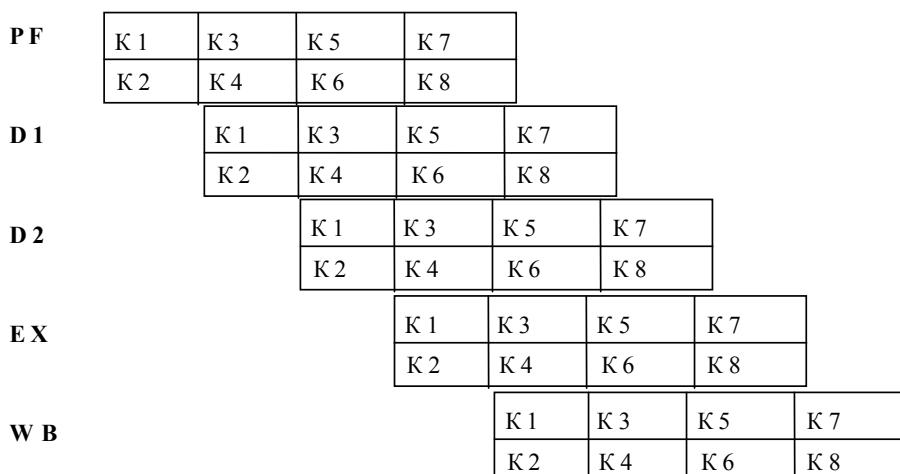

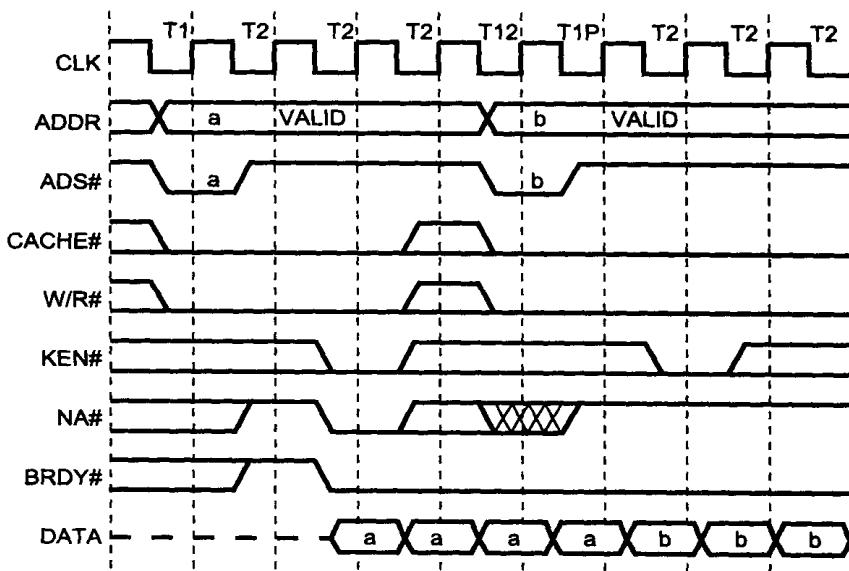

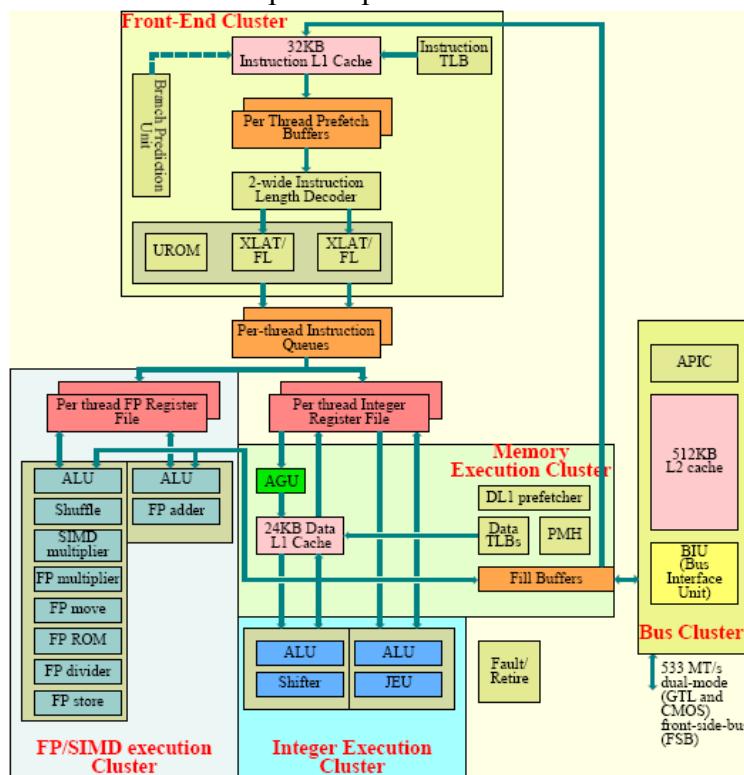

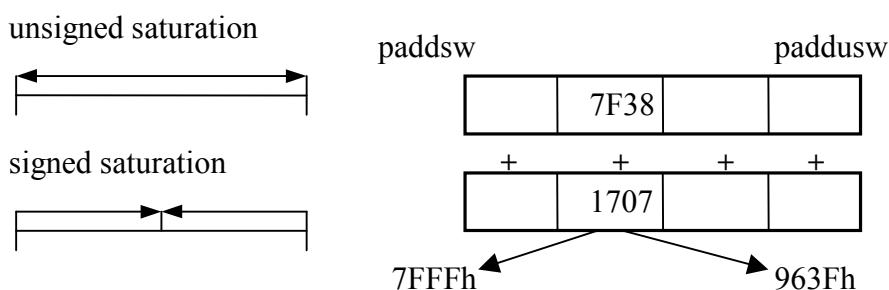

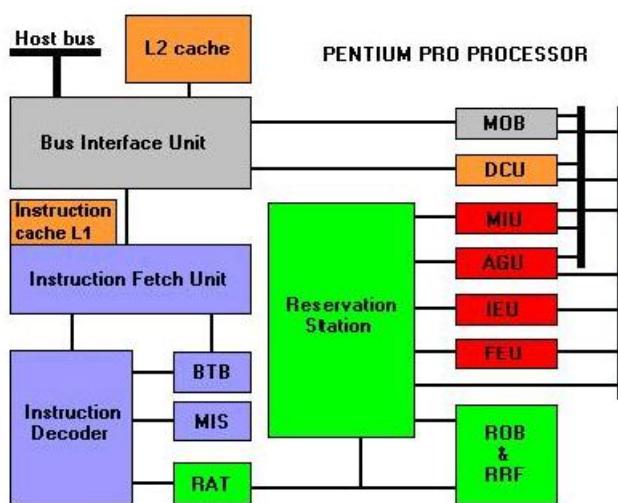

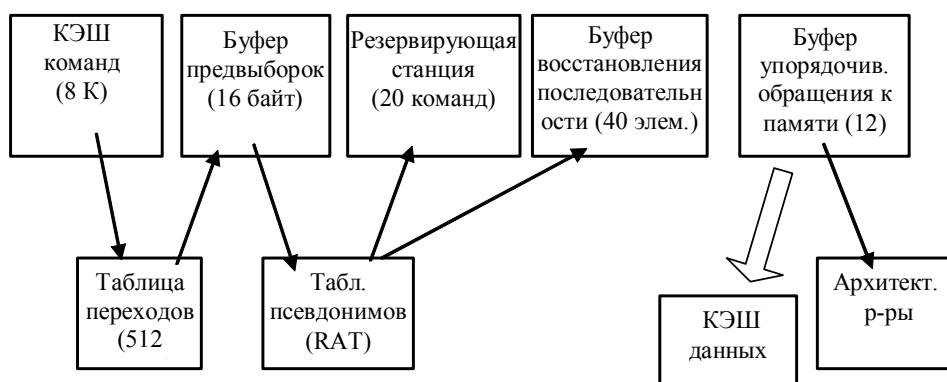

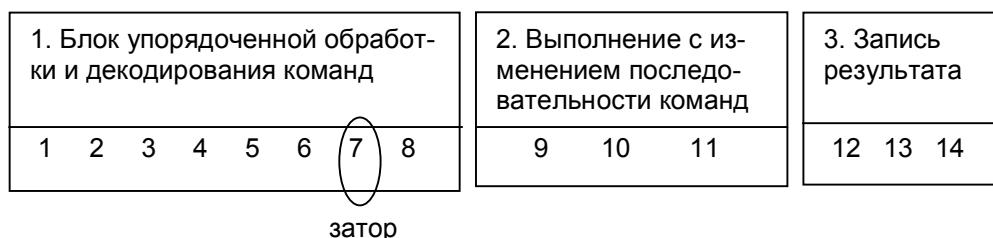

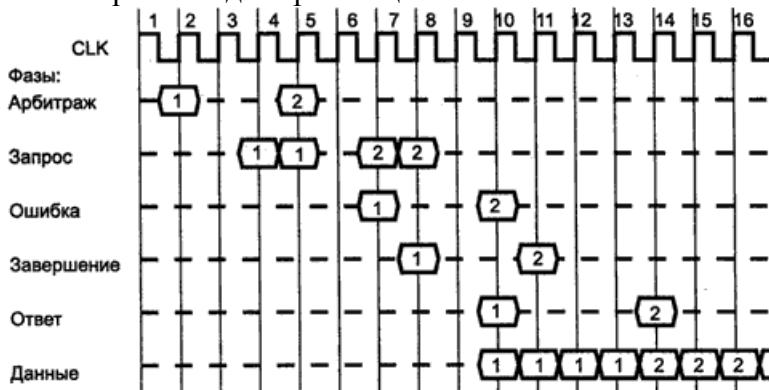

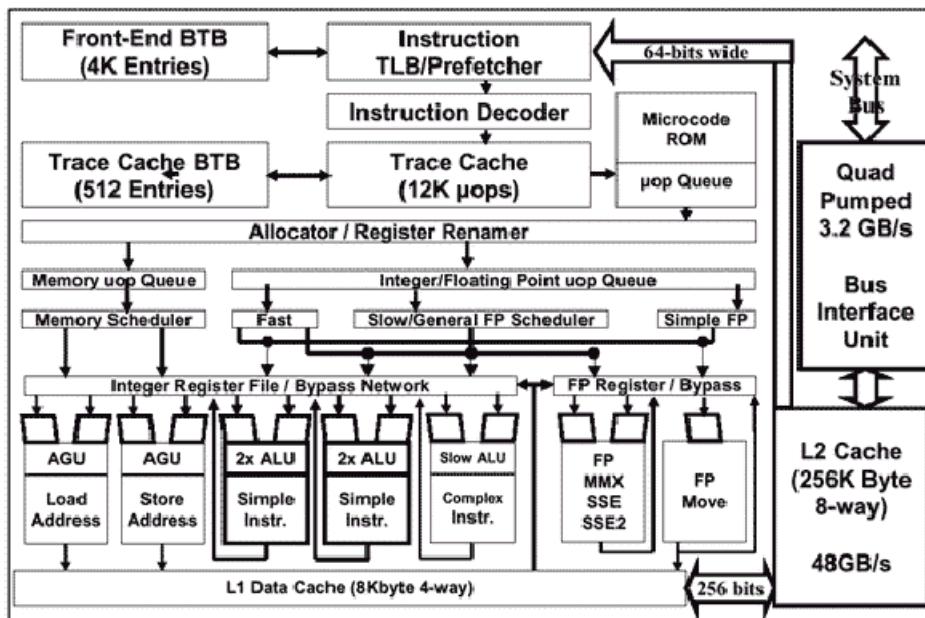

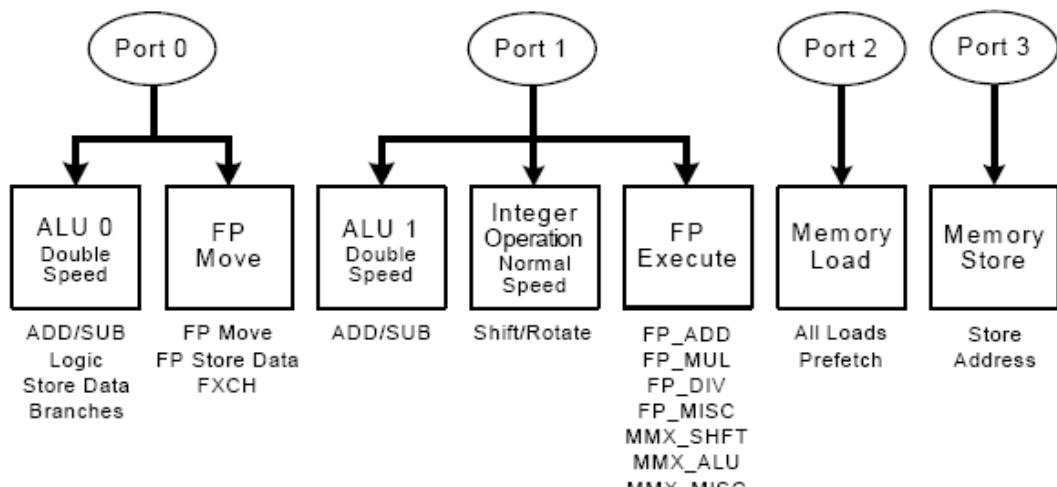

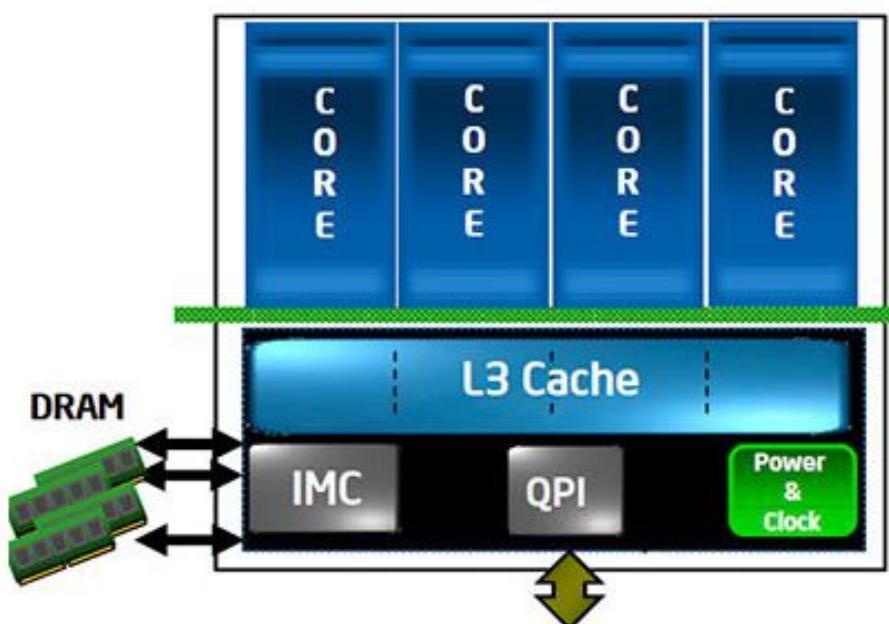

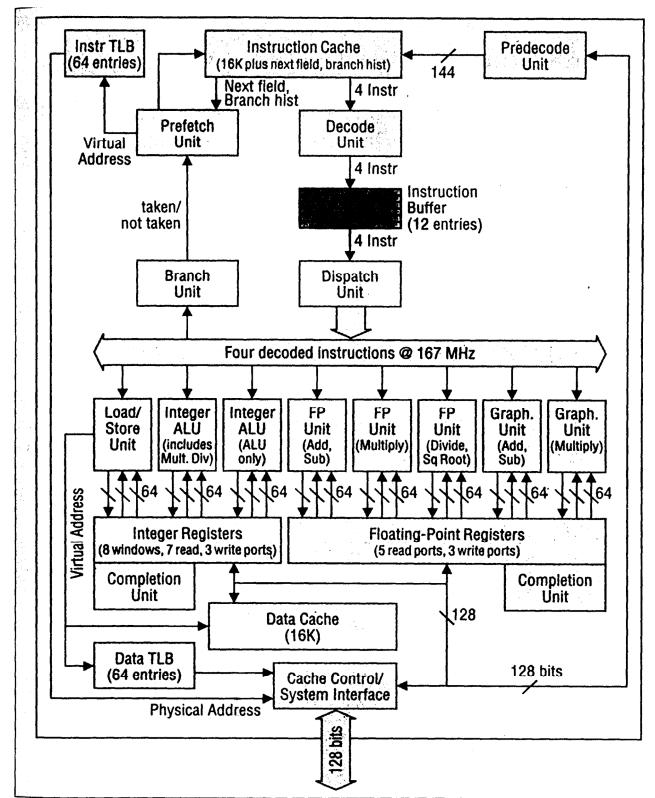

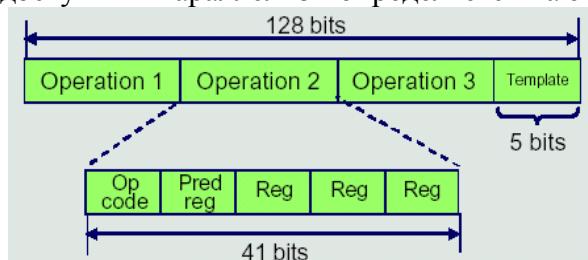

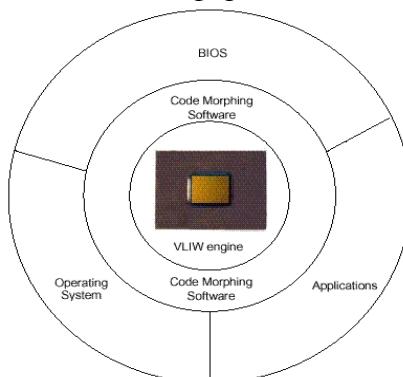

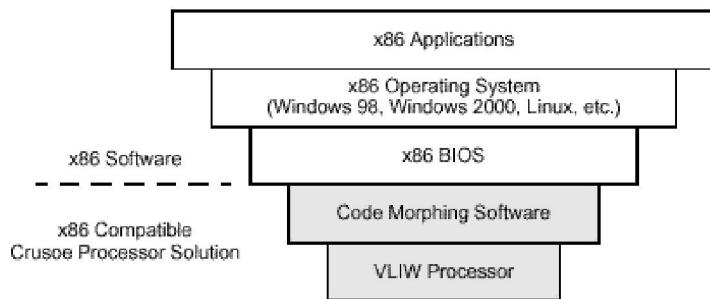

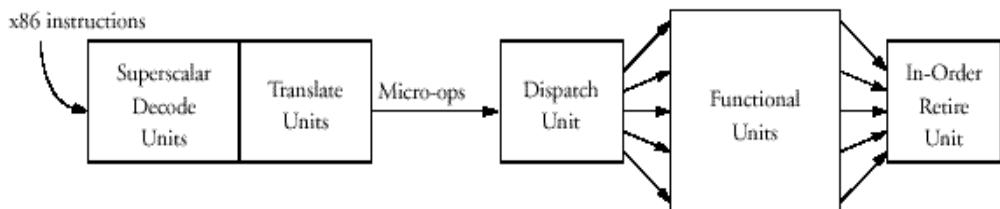

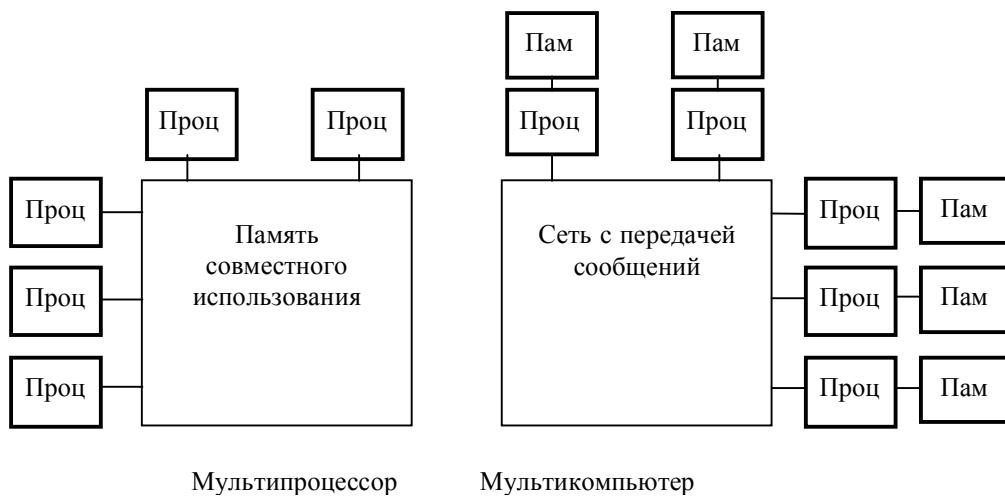

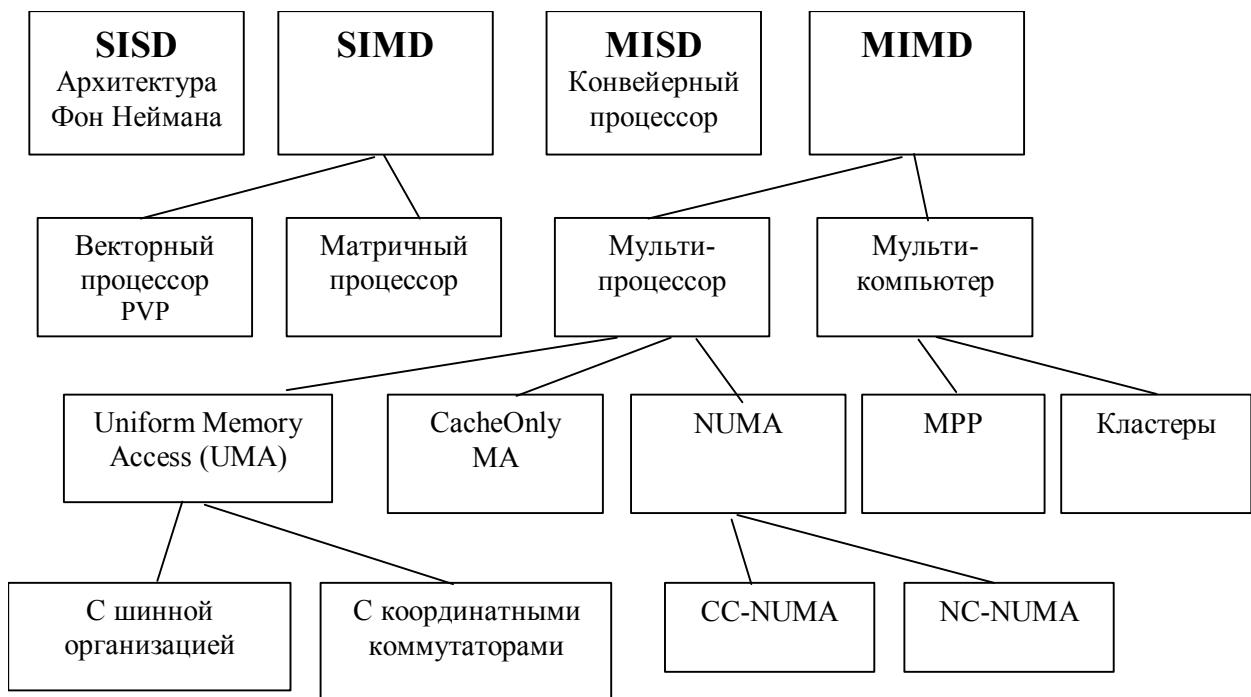

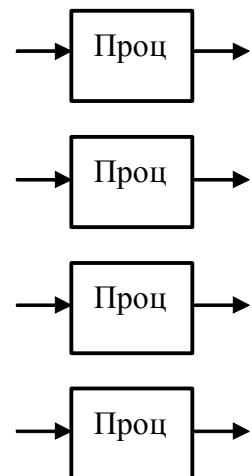

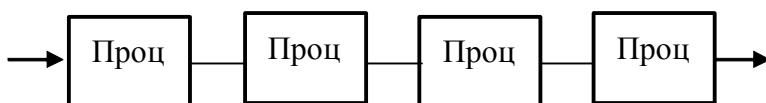

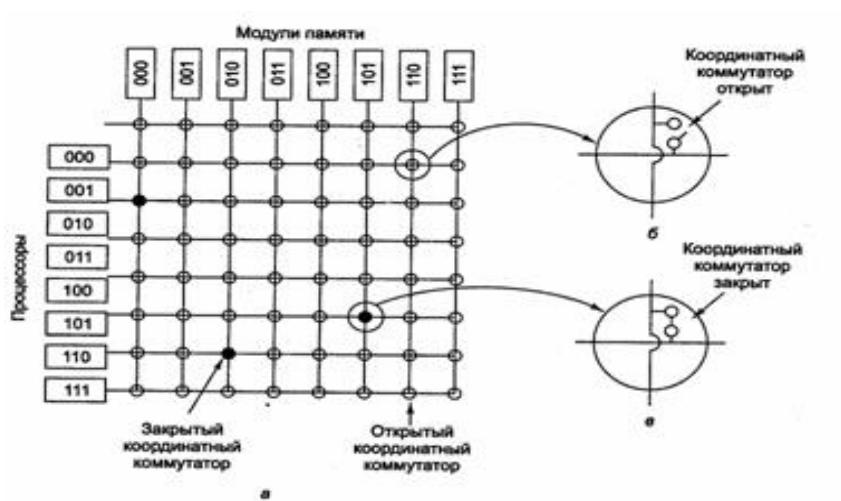

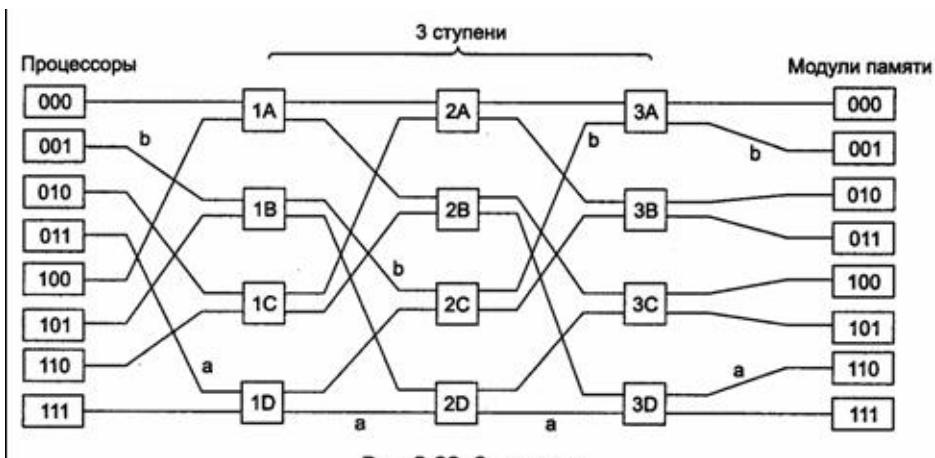

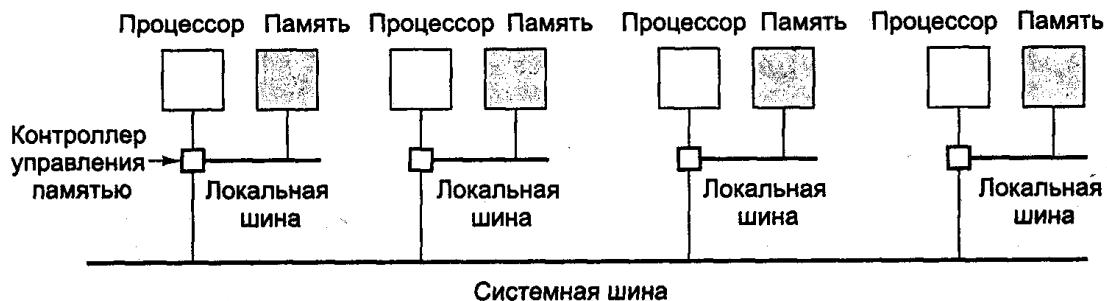

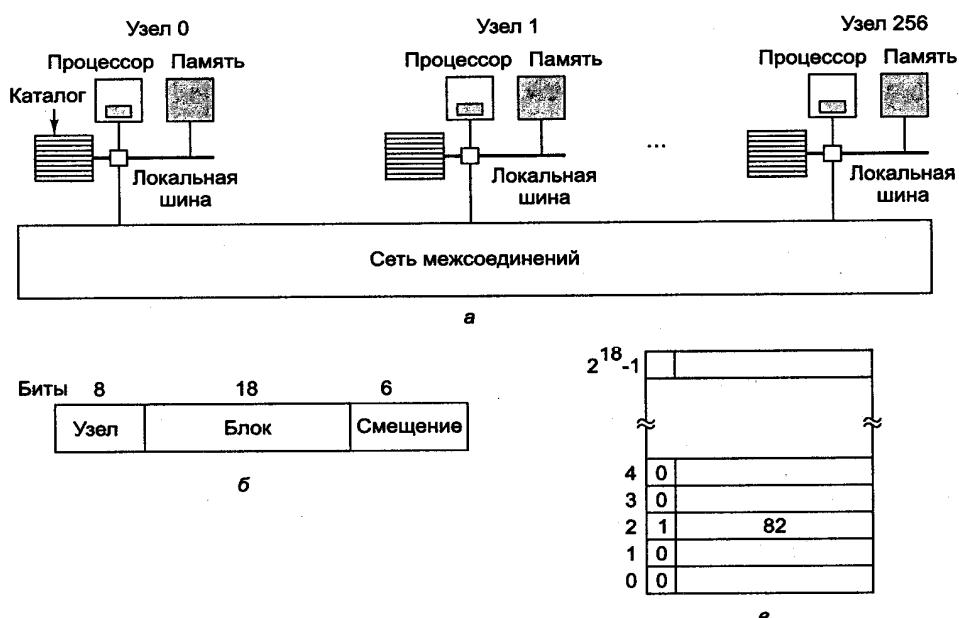

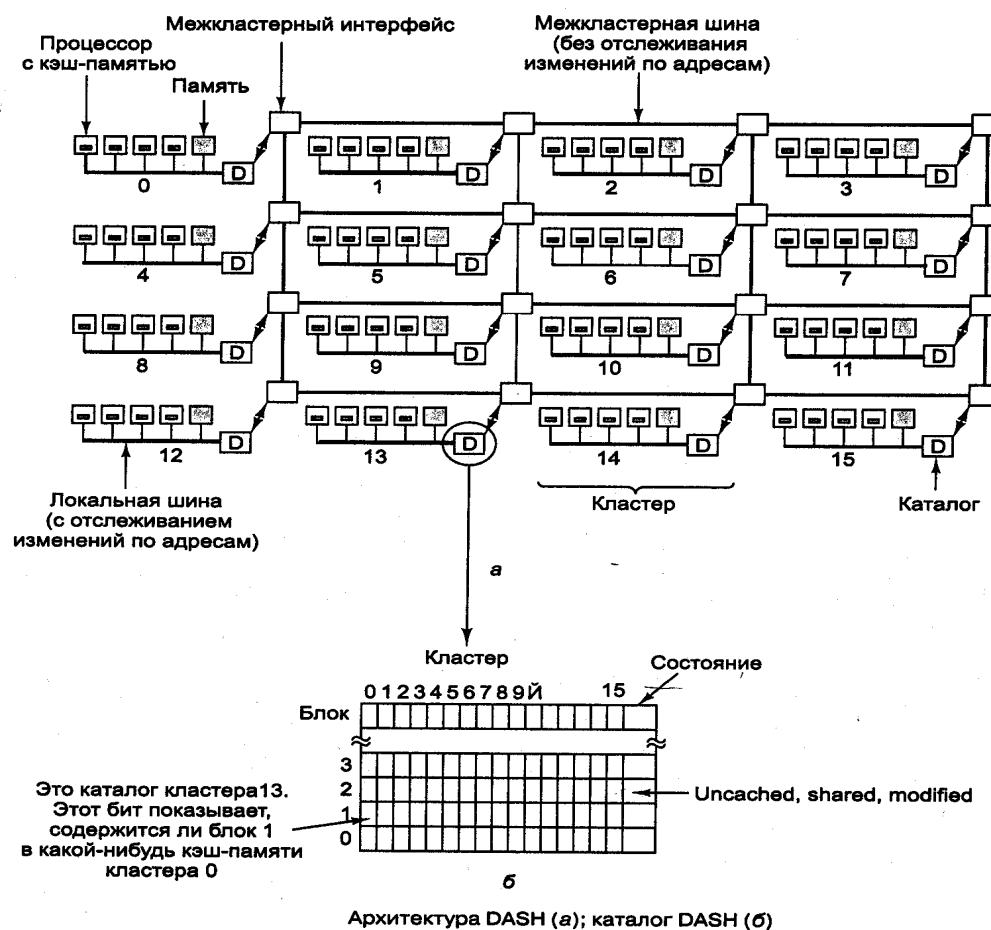

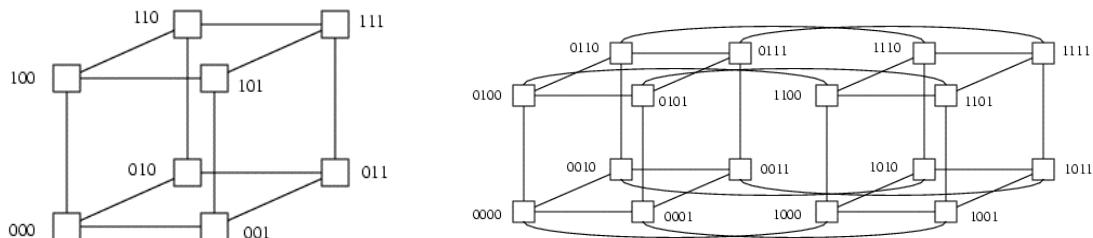

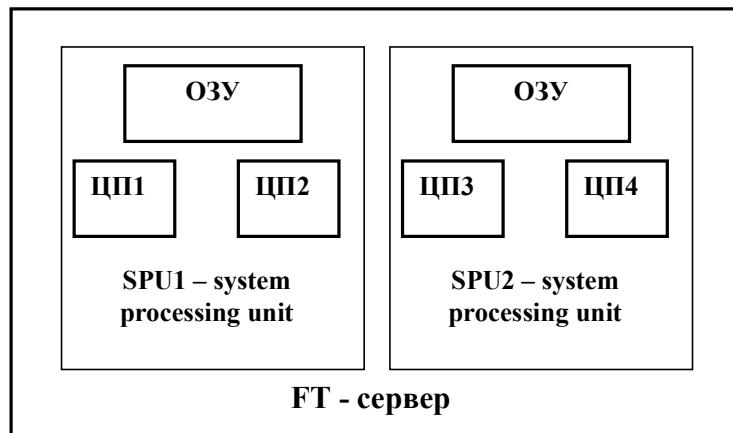

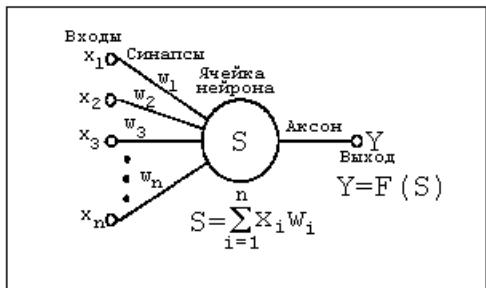

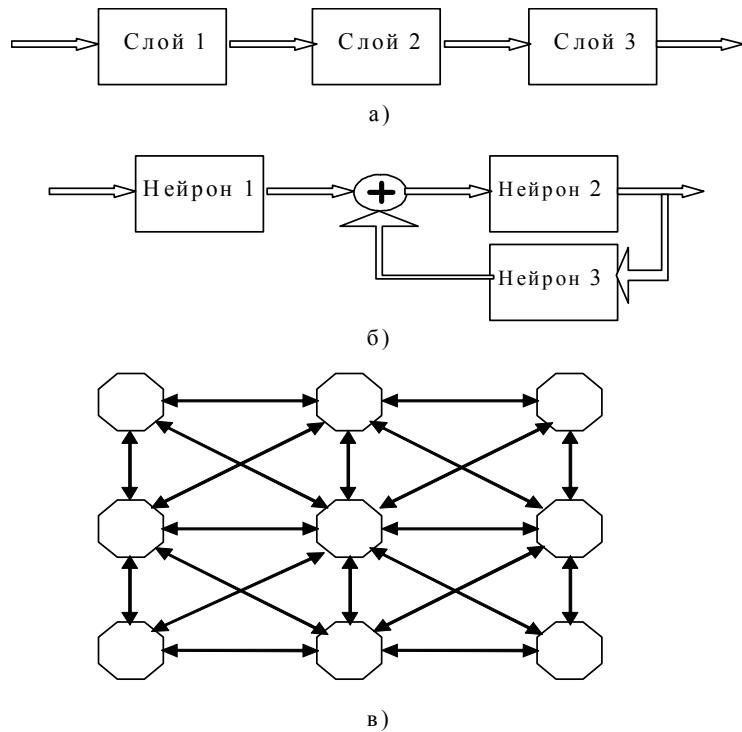

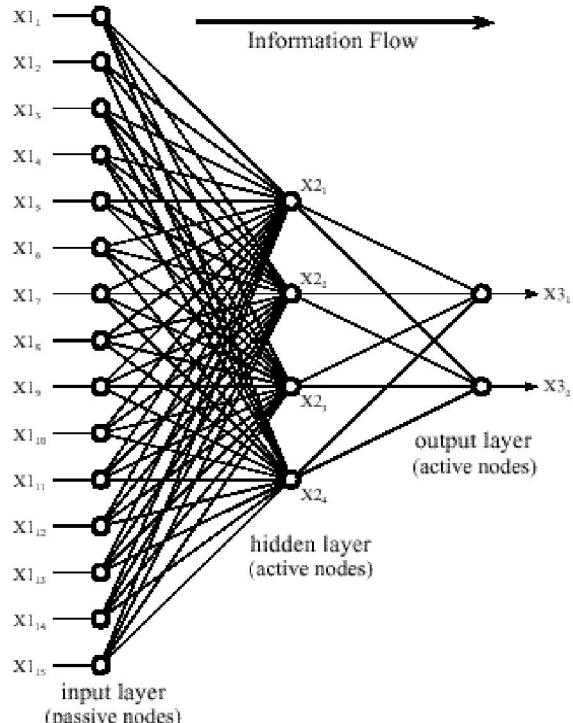

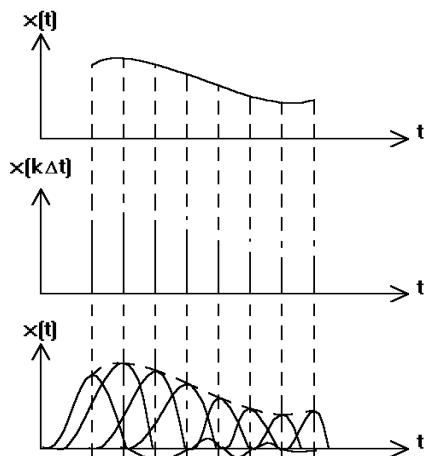

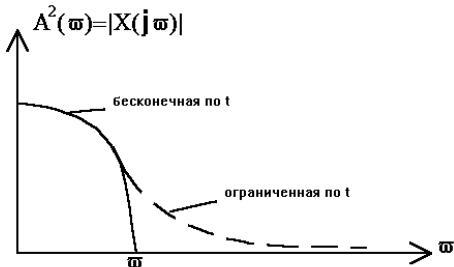

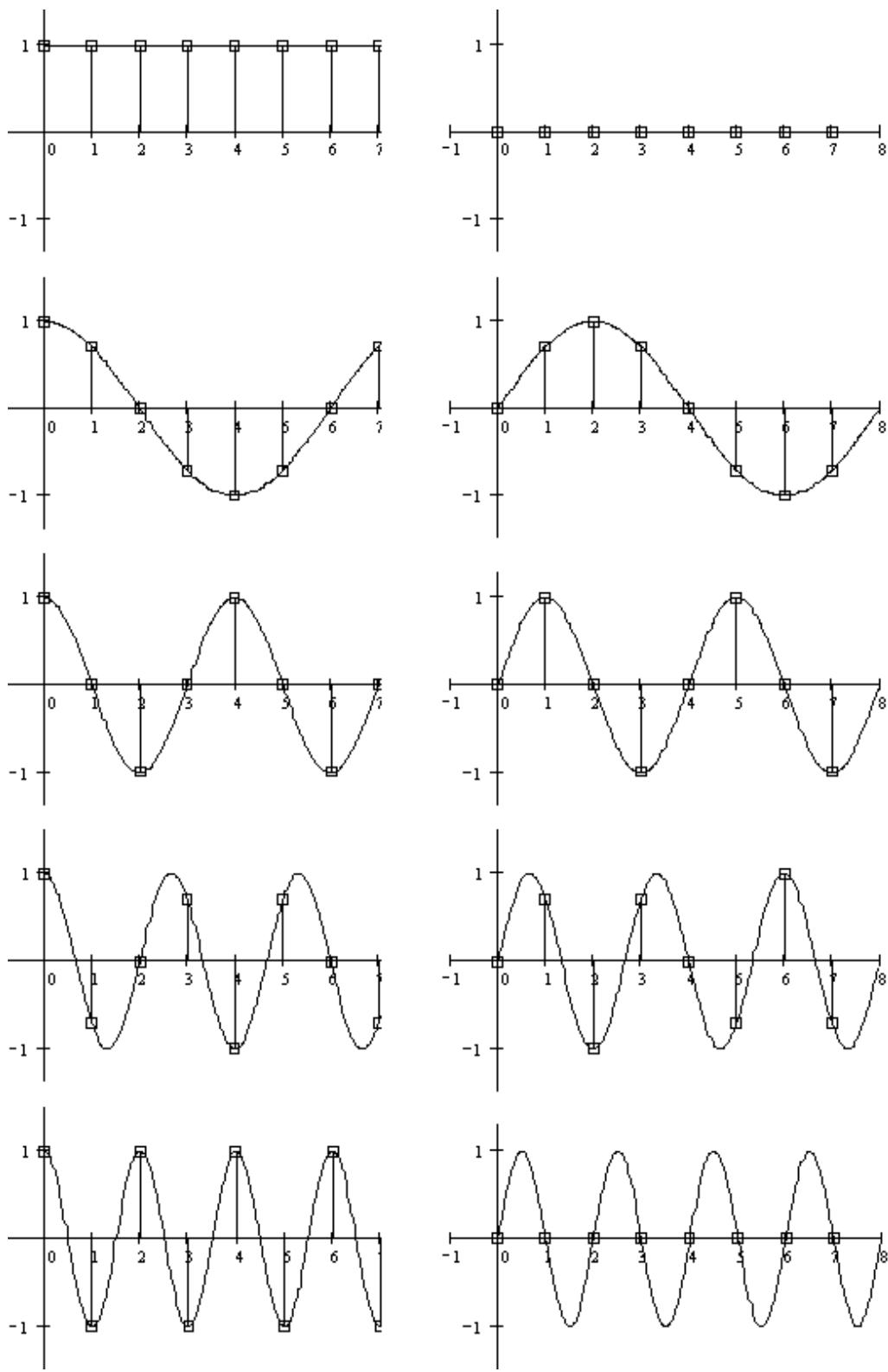

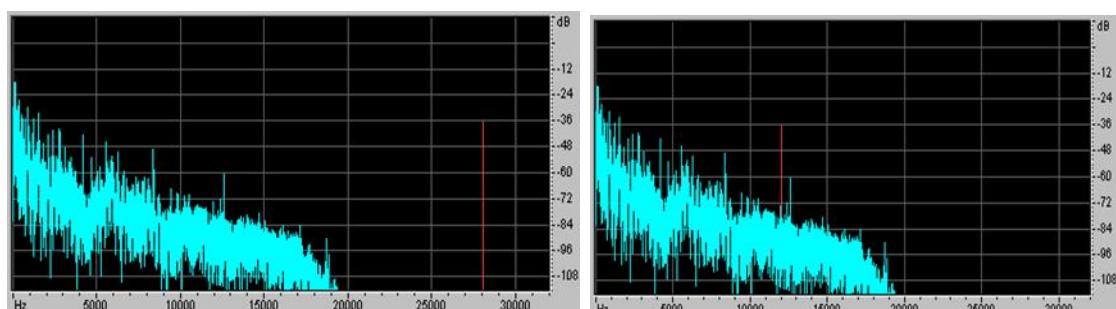

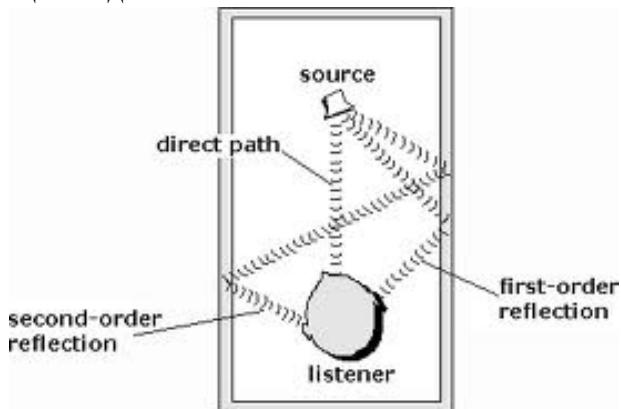

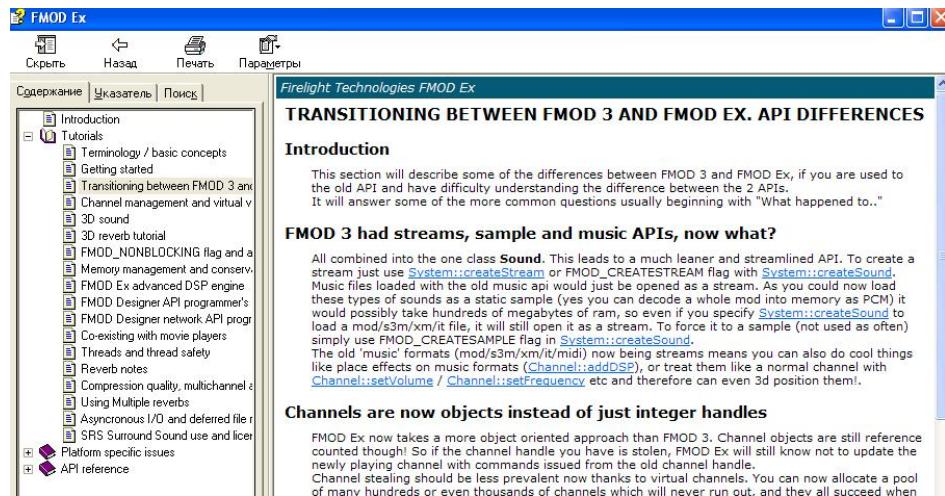

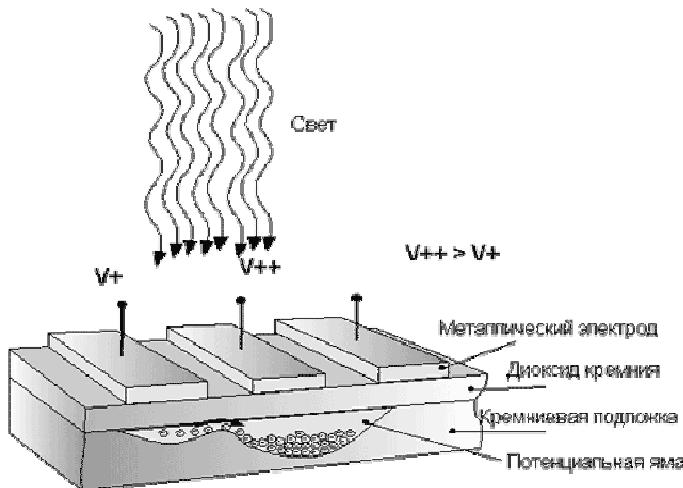

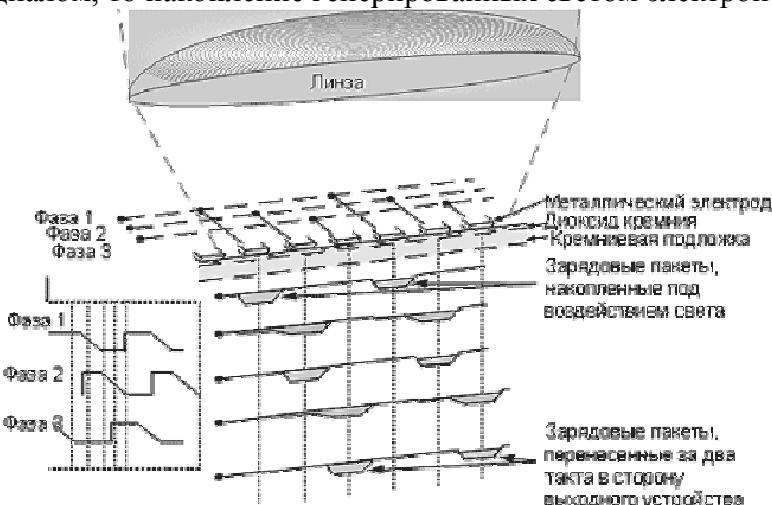

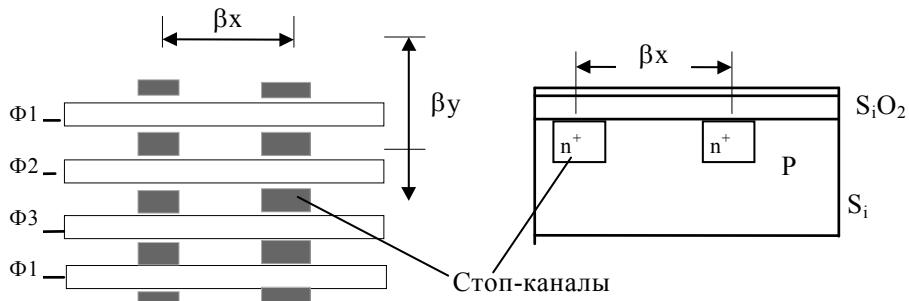

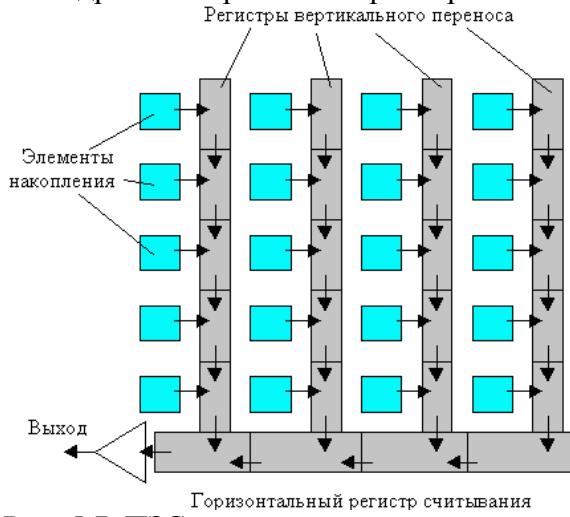

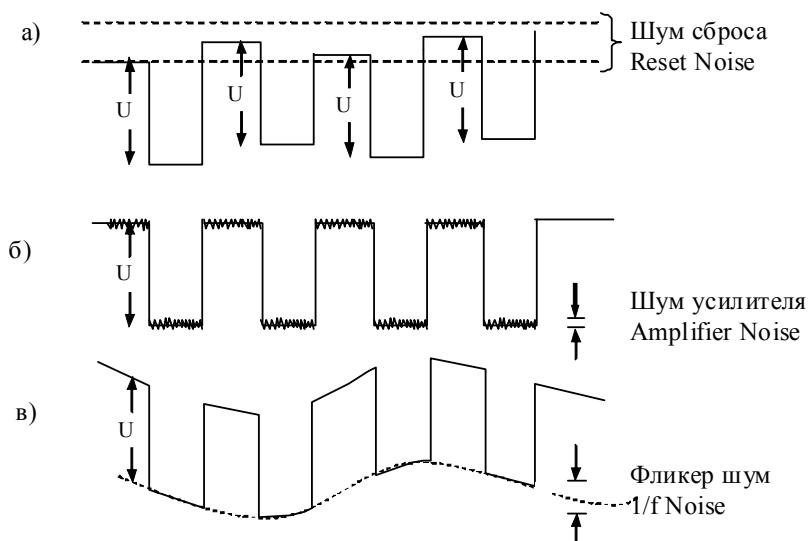

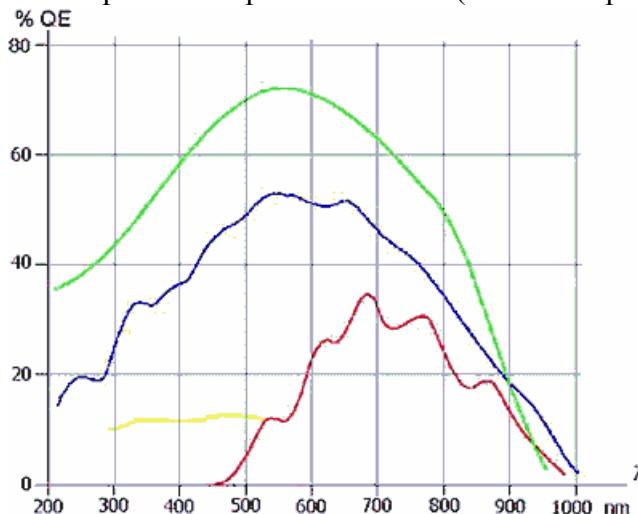

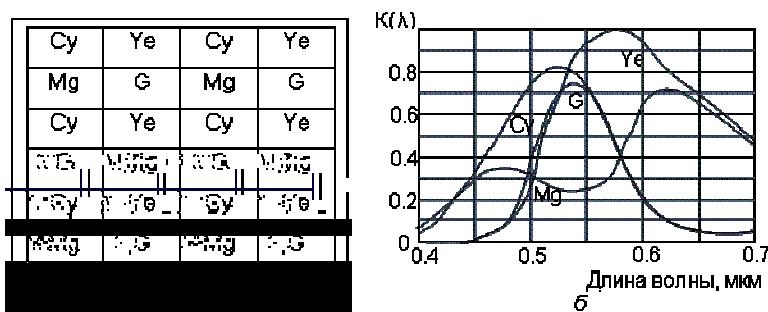

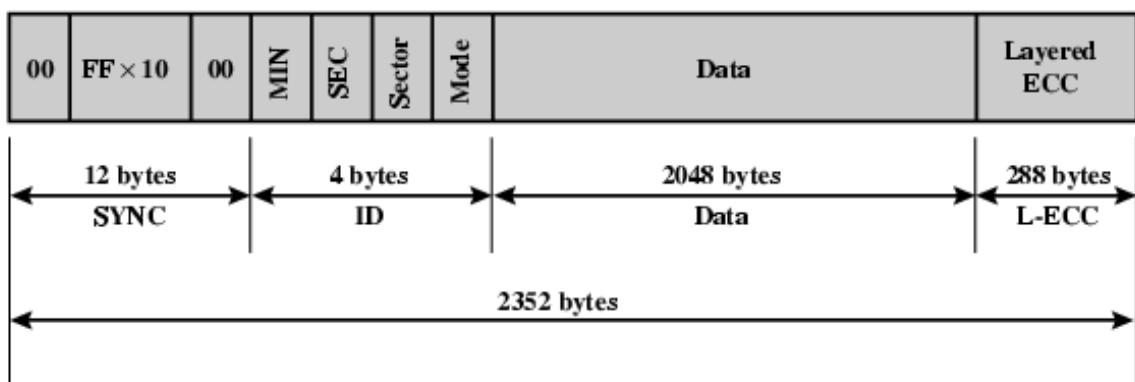

Рассмотрим буфер целевых адресов перехода, который буферизует команды из прогнозируемой ветви. Пусть к нему выполняется обращение по адресу команды безусловного перехода. Единственной задачей этой команды безусловного перехода является замена текущего значения счетчика команд. В этом случае, когда буфер адресов регистрирует попадание и показывает, что переход безусловный, конвейер просто может заменить команду, которая выбирается из кэш-памяти (это и есть сама команда безусловного перехода), на команду из буфера. В некоторых случаях таким